基于SOPC的M8051嵌入式調試器設計

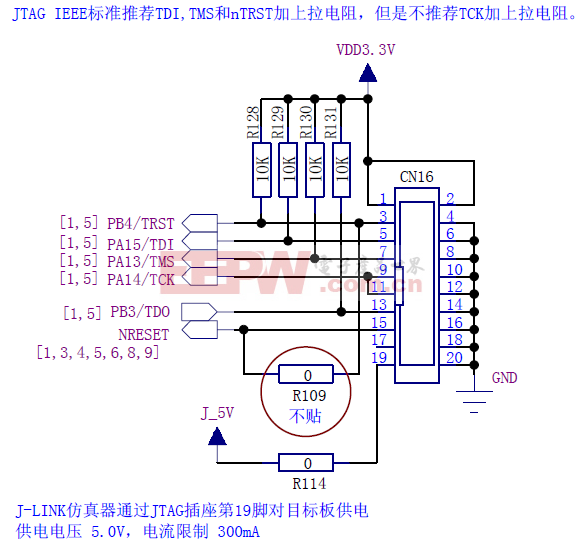

本文中的軟件部分主要負責調試協議數據的生成和傳送,具體的調試命令解析和JTAG邊界掃描時序的產生,全部由硬件實現,保證了調試效率的最大化。

3 M8051調試系統的測試

3.1 測試環境

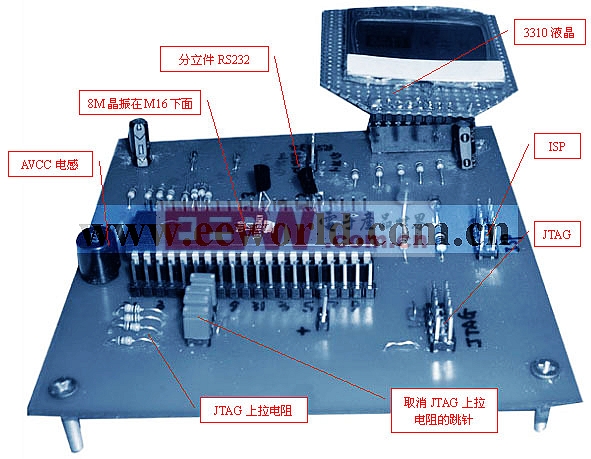

測試環境包括軟件環境和硬件環境。軟件環境包括Kell C51編譯器和Xilinx ISE Design Suite;硬件環境包括PC機、本文開發的調試器電路板和基于M8051處理器的目標板。測試環境如圖7所示。

3.2 調試系統的功能測試

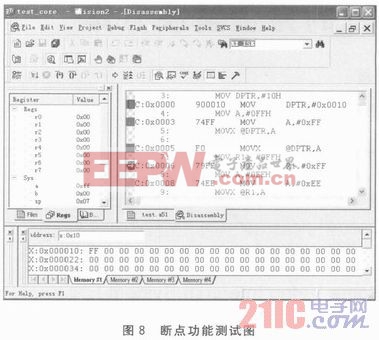

功能測試的項目主要包括:涮試開始/停止、單步運行、斷點、讀寫寄存器、瀆寫存儲器等。經測試,以上調試操作穩定可靠。以斷點操作為例,斷點操作是軟件調試過程中最重要的手段之一,本文斷點功能經測試完全可靠。測試結果如圖8所示。CPU從PC指針為零處開始執行,到達斷點地址0x0006處停止執行,并將處理器的最新狀態更新到用戶界面上。

3.3 調試器的主要參數

本調試器采用USB2.0全速(12 Mbps)接口,調試器內部M8051處理器主頻為48 MHz,JTAG協議數據收發速度達到8 Mbps。采用Spartan-6 xc6slx16 FPGA芯片實現,FPGA資源使用情況如下:可配置邏輯單元Slice1439個,占該資源總數的63%;嵌入式存儲模塊BLOCKRAM 144 KB,占該資源總數的14%;I/O接口數24個,占該資源總數的13%;時鐘管理模塊DCM 1個,占該資源總數的25%。

結語

本文給出的基于USB接口、以單一FPGA芯片實現的M8051嵌入式淵試器系統,不僅突破了傳統調試器的速度瓶頸,而且大大簡化了系統的復雜度。經測試,本調試器系統能夠高效地完成M8051處理器的軟件開發,是一種易于被開發者接受的高性價比、實用的調試器方案。

評論