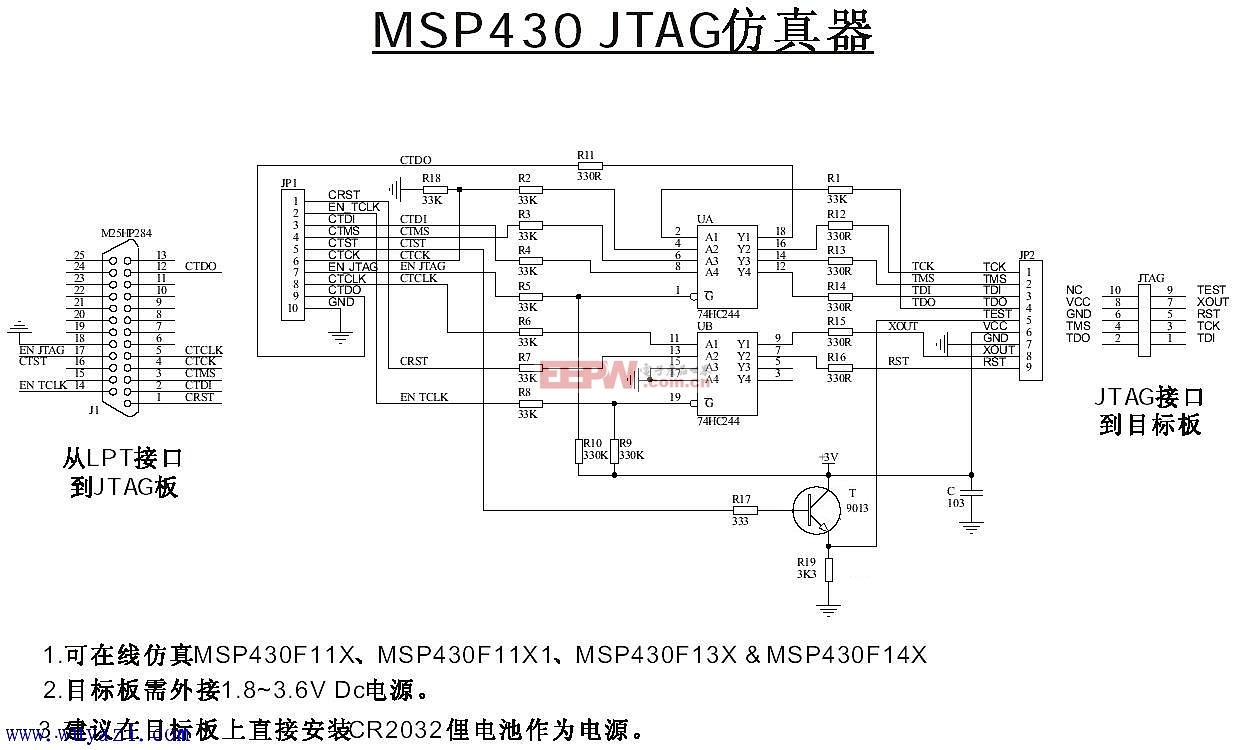

JLink和JTAG接口引腳定義和使用方法

JTAG各類接口針腳定義、含義

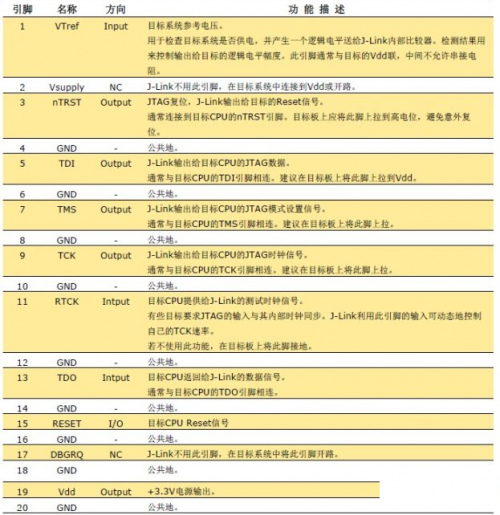

本文引用地址:http://www.104case.com/article/201712/372873.htm一、引腳定義

Test Clock Input (TCK) -----強(qiáng)制要求1

TCK在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TCK為TAP的操作提供了一個(gè)獨(dú)立的、基本的時(shí)鐘信號(hào),TAP的所有操作都是通過這個(gè)時(shí)鐘信號(hào)來驅(qū)動(dòng)的。

Test Mode SelecTIon Input (TMS) -----強(qiáng)制要求2

TMS信號(hào)在TCK的上升沿有效。TMS在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TMS信號(hào)用來控制TAP狀態(tài)機(jī)的轉(zhuǎn)換。通過TMS信號(hào),可以控制TAP在不同的狀態(tài)間相互轉(zhuǎn)換。

Test Data Input (TDI) -----強(qiáng)制要求3

TDI在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TDI是數(shù)據(jù)輸入的接口。所有要輸入到特定寄存器的數(shù)據(jù)都是通過TDI接口一位一位串行輸入的(由TCK驅(qū)動(dòng))。

Test Data Output (TDO) -----強(qiáng)制要求4

TDO在IEEE1149.1標(biāo)準(zhǔn)里是強(qiáng)制要求的。TDO是數(shù)據(jù)輸出的接口。所有要從特定的寄存器中輸出的數(shù)據(jù)都是通過TDO接口一位一位串行輸出的(由TCK驅(qū)動(dòng))。

Test Reset Input (TRST) ----可選項(xiàng)1

這個(gè)信號(hào)接口在IEEE 1149.1標(biāo)準(zhǔn)里是可選的,并不是強(qiáng)制要求的。TRST可以用來對(duì)TAPController進(jìn)行復(fù)位(初始化)。因?yàn)橥ㄟ^TMS也可以對(duì)TAP Controll進(jìn)行復(fù)位(初始化)。所以有四線JTAG與五線JTAG之分。

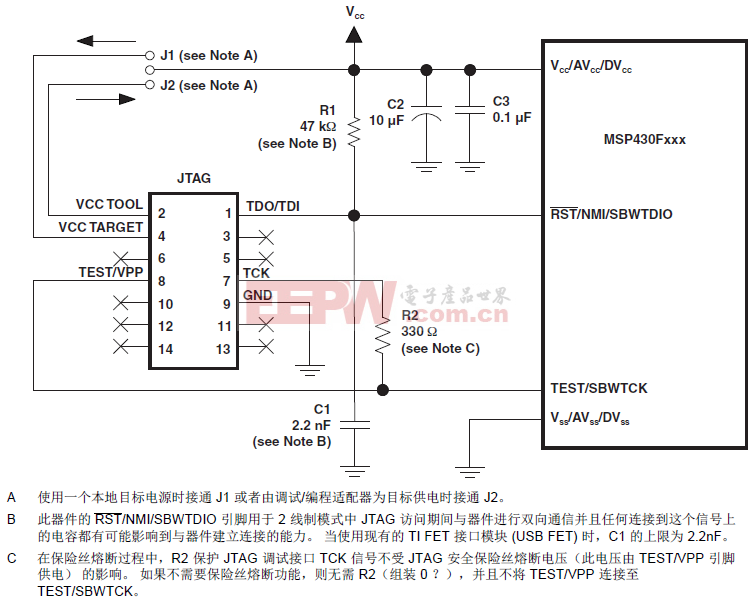

(VTREF) -----強(qiáng)制要求5

接口信號(hào)電平參考電壓一般直接連接Vsupply。這個(gè)可以用來確定ARM的JTAG接口使用的邏輯電平(比如3.3V還是5.0V?)

Return Test Clock ( RTCK) ----可選項(xiàng)2

可選項(xiàng),由目標(biāo)端反饋給仿真器的時(shí)鐘信號(hào),用來同步TCK信號(hào)的產(chǎn)生,不使用時(shí)直接接地。

System Reset ( nSRST)----可選項(xiàng)3

可選項(xiàng),與目標(biāo)板上的系統(tǒng)復(fù)位信號(hào)相連,可以直接對(duì)目標(biāo)系統(tǒng)復(fù)位。同時(shí)可以檢測(cè)目標(biāo)系統(tǒng)的復(fù)位情況,為了防止誤觸發(fā)應(yīng)在目標(biāo)端加上適當(dāng)?shù)纳侠娮琛?/p>

說明:

1腳:通常連接到目標(biāo)板的vdd,用來檢測(cè)目標(biāo)系統(tǒng)是否供電;檢測(cè)原理上圖中有簡(jiǎn)單的說明。

2腳:原版的JLink這個(gè)引腳沒有使用,不提供Vsupply輸出,而很多改造版的JLink通過跳線選擇從該引腳輸出3.3V的電壓給外邊,我的就是這樣的。

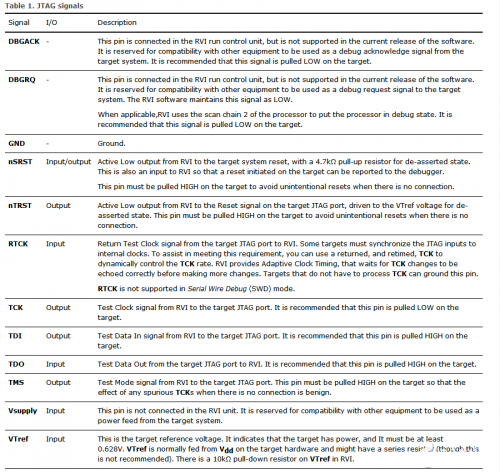

JTAG interface signals

The following table describes the signals on the JTAG interfaces:

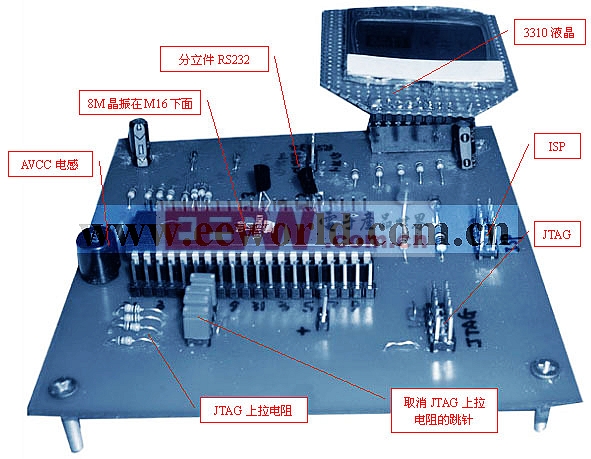

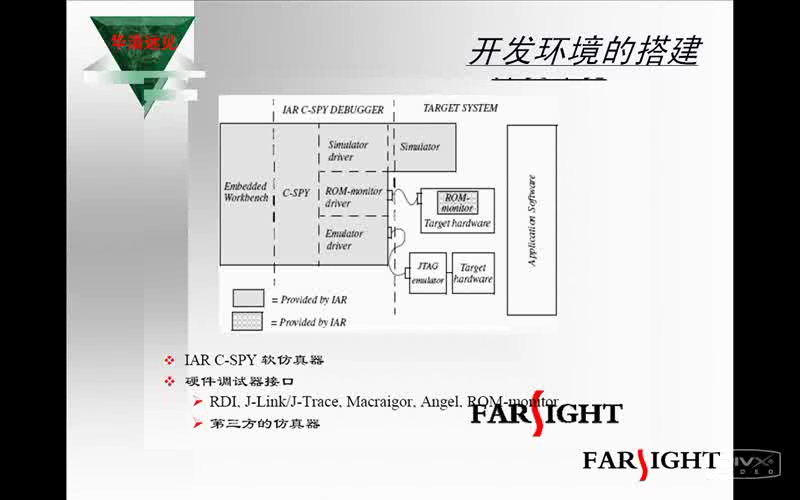

ARM系統(tǒng)的JTAG接口的設(shè)計(jì)不當(dāng)往往使硬件系統(tǒng)無法調(diào)試,所以在設(shè)計(jì)ARM系統(tǒng)前要先熟悉ARM系統(tǒng)的JTAG接口的定義和常見問題。

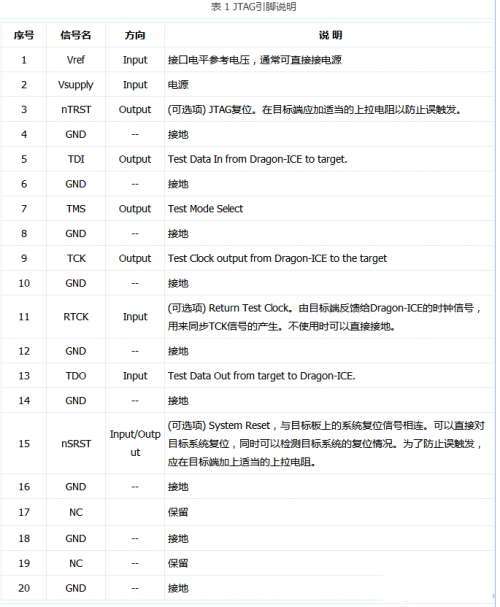

1.ARM系統(tǒng)的JTAG接口是如何定義的? 每個(gè)PIN又是如何連接的?

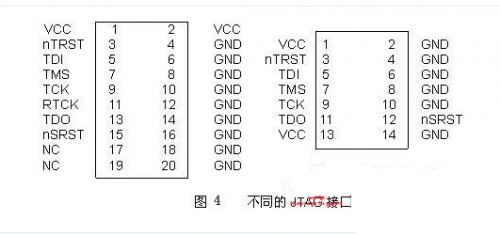

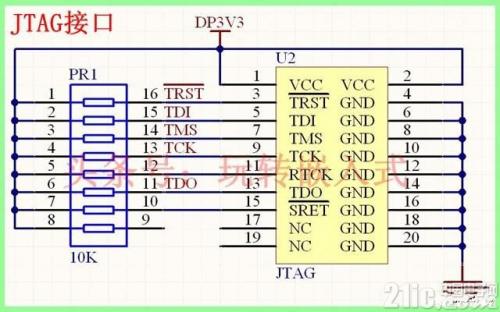

下圖是JTAG接口的信號(hào)排列示意:

接口是一個(gè)20腳的IDC插座。下表給出了具體的信號(hào)說明:

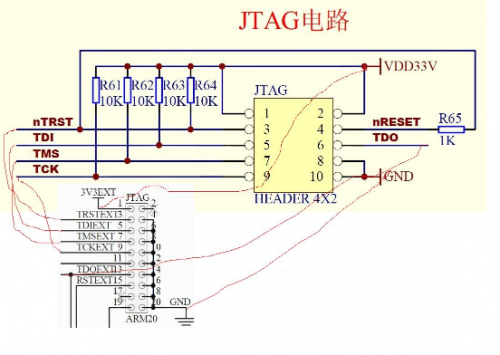

目標(biāo)系統(tǒng)如何設(shè)計(jì)?

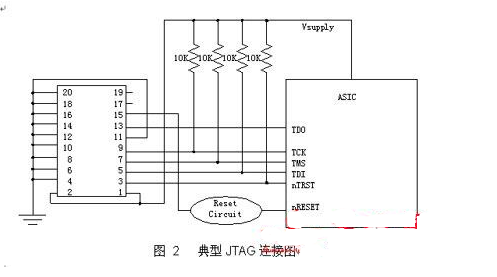

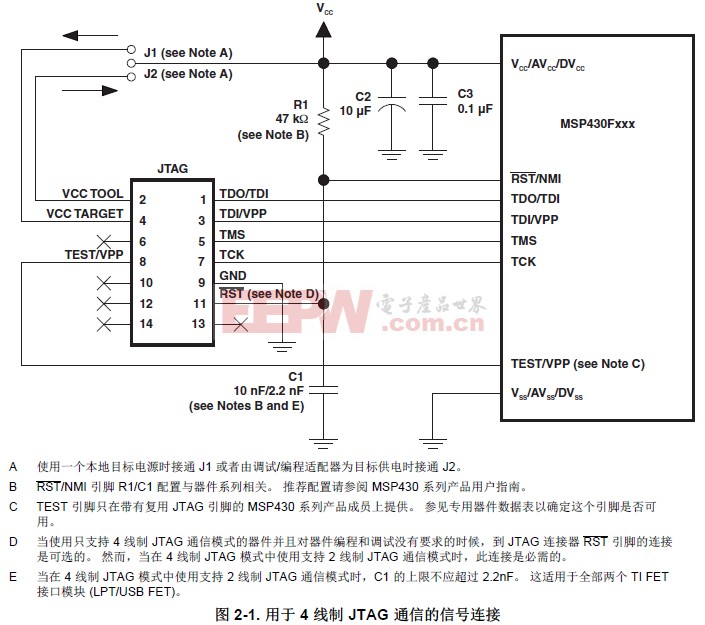

目標(biāo)板使用與Dragon-ICE一樣的20腳針座,信號(hào)排列見表1。RTCK和 nTRST這兩個(gè)信號(hào)根據(jù)目標(biāo)ASIC有否提供對(duì)應(yīng)的引腳來選用。nSRST則根據(jù)目標(biāo)系統(tǒng)的設(shè)計(jì)考慮來選擇使用。下面是一個(gè)典型的連接關(guān)系圖:

復(fù)位電路中可以根據(jù)不同的需要包含上電復(fù)位、手動(dòng)復(fù)位等等功能。如果用戶希望系統(tǒng)復(fù)位信號(hào)nSRST能同時(shí)觸發(fā)JTAG口的復(fù)位信號(hào)nTRST,則可以使用一些簡(jiǎn)單的組合邏輯電路來達(dá)到要求。后面給出了一種電路方案的效果圖。

在目標(biāo)系統(tǒng)的PCB設(shè)計(jì)中,最好把JTAG接口放置得離目標(biāo)ASIC近一些,如果這兩者之間的連線過長(zhǎng),會(huì)影響JTAG口的通信速率。

另外電源的連線也需要加以額外考慮,因?yàn)镈ragon-ICE要從目標(biāo)板上吸取超過100mA的大電流。最好能有專門的敷銅層來供電,假如只能使用連線供電的話,最小線寬不應(yīng)小于10mil (0.254mm)。

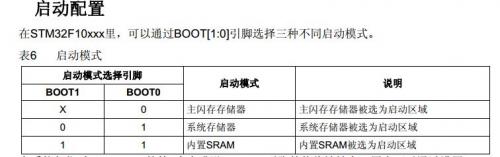

14腳JTAG如何與20JTAG連接?

Dragon-ICE使用工業(yè)標(biāo)準(zhǔn)的20腳JTAG插頭,但是有些老的系統(tǒng)采用一種14腳的插座。這兩類接口的信號(hào)排列如下:

這兩類接口之間的信號(hào)電氣特性都是一樣的,因此可以把對(duì)應(yīng)的信號(hào)直接連起來進(jìn)行轉(zhuǎn)接。Dragon-ICE配備這種轉(zhuǎn)接卡,隨機(jī)配備。

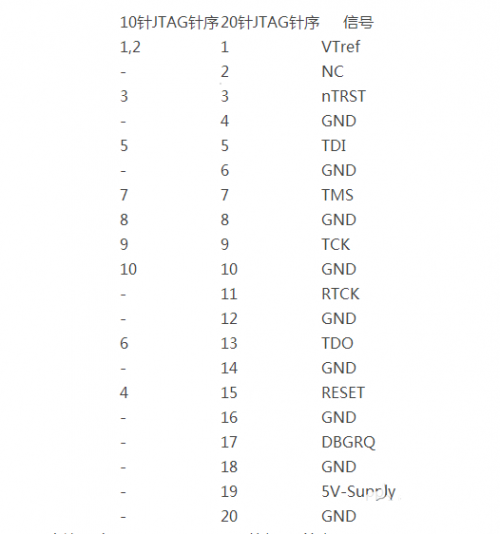

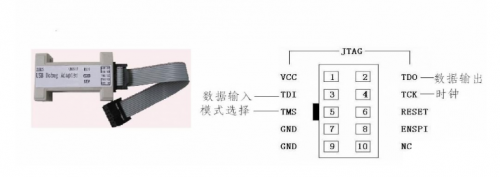

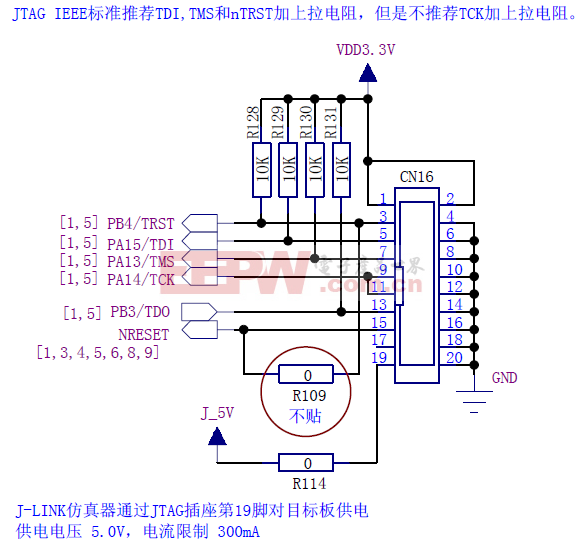

JLINK 10針J和20針JTAG接口連接方法

下面說一下接法,其實(shí)根本不需要什么轉(zhuǎn)接板什么的,直接把相應(yīng)的幾根線對(duì)接就可以用了,所以要參考電路圖,上面為TQ2440開發(fā)板的JTAG電路圖,下面為JLINK的20針電路圖,下面的JLINKV7電路圖是標(biāo)準(zhǔn)接口,網(wǎng)上到處都能找到

實(shí)際上只需要接4跟線,4號(hào)是自連回路,不需要接,1,2接的都是1管腳,而8,10接的是GND,也可以不接。

評(píng)論