基于ARM處理器的HDLC通信的DMA實現

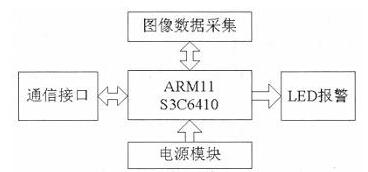

1.3 緩沖描述符(BD)

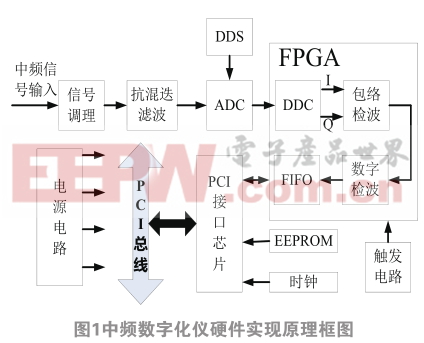

緩沖描述符是S3C5410B使用的一種數據結構,通常構成循環鏈表。HDMA引擎可以直接讀取結構的信息,用戶通過填寫這些結構中的域去控制HDMA的運行行為。如圖2所示,每個BD包括4個域:

①數據緩存指針(data buffer pointer)。第31位標識主權(ownership)關系,表示當前的BD在DMA(1)控制器和CPU(0)之間的所屬關系,通常在發送和接收時要對其檢查。對于數據長度,通常在發送時寫入BD的幀長度域,DMA引擎會根據其發送相應長度的數據。接收數據長度會自動寫入這個域。

②保留域。發送BD(Tx),低8位表示發送控制(如前同步信號、CRC模式、BIG/LITTLE端選擇等);接收BD(Rx),保留未用。

③長度域。發送BD,用戶寫入發送幀的數據長度;接收BD,DMA控制器寫入接收幀的數據長度。

④Next BD指針。指向下一個BD,收發BD各自構成一組BD鏈。

HDMA控制器在使用過一個BD后,會自動讀入下一個BD,裝入HDMA指針寄存器(HDMAXxPTR)。使用指針gpXxBDStart,指示當前的可用BD位置。在設備中定義為全局變量(X表示T或R)。

1.4 重要的數據類型

BD結構的定義如圖2所示。

typedef struct BD{

U32 BufferData Ptr;

//數據緩存區指針,其中第31位標識BD的所有權

U32 Reserved;

//發送BD控制位,定義發送時操作的模式,接收BD保留

U32 StatusLength;

//運行狀態,在ISR中檢測,也定義對應的數據緩存區的長度

struct BD *NextBD;

//下一個BD指針

}sBuffer Descriptor;

HDLC幀(Frame)定義(如表1):

typedef struct HDLCFRAME{

U8 address[4]; //地址

U8 control; //控制信息通道為FFH

U8 information[1505]; //信息域,有效的數據

}sHdlcFrame;

HDLC設備結構定義:

typedef struct HDLC_Device {

U32 HDLC_Port; /HDLC通信號

U32 HDLC_Baud; //HDLC波特率

U32 HDLC_Data_format;

//HDLC數據格式,NRZ,NRZI,FM0,FM1,Manchester

//……時鐘選擇(發送/接收時鐘源)……

sBufferDescriptor gpTxBDStart;/*當前的發送BD指針Start of TX BDs*/

sBufferDescriptor *gpRxBDStart; /*當前的接收BD指針Start of RX BDs */

//……狀態統計信息(Abort,CRC error,Null list)……

}Hdle_End_Device;

由于在中斷服務程序入口無法傳遞參數,故定義設備為全局變量,程序設計中使用指針傳遞,提高效率。

評論