基于ARM處理器的HDLC通信的DMA實現

目前在嵌入式產品開發設計中,通常是在OS(Operating System)廠商提供的BSP基礎上進行開發工作;對于底層硬件的操作,程序設計人員很少關注或只是少量的修改。實際上很多產品,我們完全可以拋開操作系統的模式,避免不必要的系統開銷,而對底層的硬件直接進行處理。這樣,可以節省資源提高利用率。當然,這樣也會人為地增加系統開發設計的難度。但是從長遠的角度看,進行這樣的設計思考還是非常必要的。現在一些產品的設計開發中,所缺少的實際上就是深入了解底層操作,這樣往往使我們丟失了創新的機會。

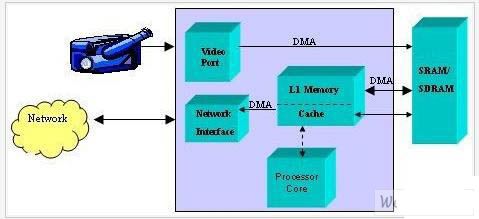

(2)DMA模式

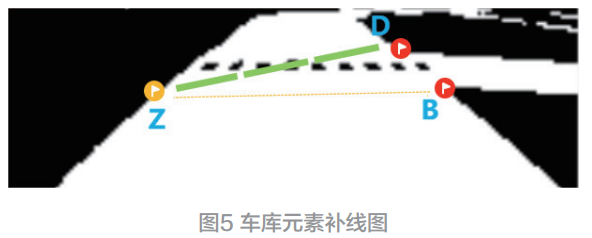

使用緩沖描述符BD(Buffer Descriptor)結構,可以實現以幀為單位對數據進行接收和發送控制。程序設計人員只需要填寫相應BD結構的域信息,配置收發模式,具體的執行細節交給DMA單元控制完成。CPU只是對每一幀進行處理,這樣在一幀收發的過程中,系統可以去處理其它的任務,有效地利用CPU資源。關鍵在于構建BD循環鏈表。同時應該注意,BD及其對應的緩沖數據區必須放在系統存儲區的非緩存區(NonCache),這可以通過設置地址的第26位為1來實現。

評論