基于ARM+FPGA的運(yùn)動(dòng)控制器設(shè)計(jì)與實(shí)現(xiàn)

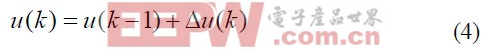

控制器的輸出為:

其中:

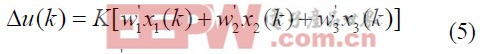

式(5)中,w'i為加權(quán)系數(shù),可在線修正。加權(quán)值的在線學(xué)習(xí)則采用規(guī)范化的學(xué)習(xí)算法,公式為式(6):

式(7)中ηi(i = I、P、D ), ηI 、ηP 、ηD 分別為積分、比例、微分的學(xué)習(xí)速率。

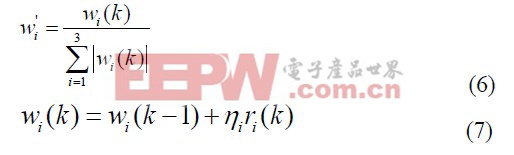

4.2 算法仿真

仿真系統(tǒng)的參數(shù):比例、積分、微分的學(xué)習(xí)速率分別為 ηP =0.40 , ηI =0.35 , ηD =0.40 ,系統(tǒng)初始誤差量值設(shè)置為1,仿真曲線如圖6 所示。從仿真結(jié)果可以看出,系統(tǒng)PID 控制參數(shù)隨系統(tǒng)的運(yùn)行在線整定,經(jīng)整定的PID 參數(shù)對(duì)系統(tǒng)進(jìn)行控制,系統(tǒng)的誤差最終趨于0。

圖6 單神經(jīng)元PID 控制誤差曲線

5 運(yùn)行結(jié)果

5.1 系統(tǒng)位移調(diào)試結(jié)果

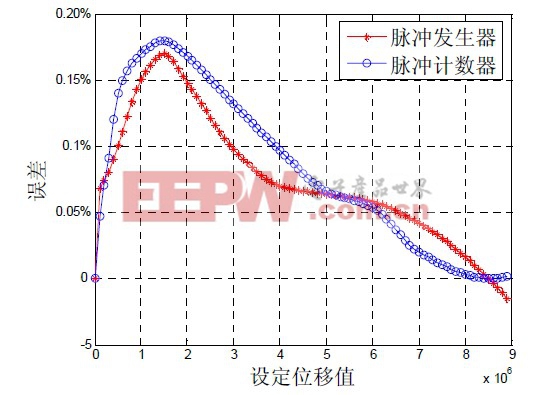

為了測(cè)試運(yùn)動(dòng)控制系統(tǒng)的位置控制效果,在電機(jī)空載時(shí)進(jìn)行了100 次試驗(yàn),圖7 所示為在實(shí)驗(yàn)室中測(cè)定的電機(jī)空載時(shí)的位移測(cè)試結(jié)果曲線圖,各試驗(yàn)數(shù)據(jù)均是取100 次實(shí)驗(yàn)數(shù)據(jù)的平均值。圖7 為各實(shí)驗(yàn)數(shù)據(jù)的曲線擬合圖。從圖中可以看出,電機(jī)空載時(shí)脈沖發(fā)生器和脈沖計(jì)數(shù)器的誤差曲線經(jīng)歷了一個(gè)積累的過(guò)程,當(dāng)誤差超過(guò)設(shè)定值0.18%時(shí)單神經(jīng)元自適應(yīng)PID控制器開(kāi)始在線整定PID 控制參數(shù),整定結(jié)果使系統(tǒng)的誤差趨于0。

圖7 系統(tǒng)位移調(diào)試結(jié)果

5.2 系統(tǒng)速度調(diào)試結(jié)果。

為了測(cè)量系統(tǒng)的速度響應(yīng)結(jié)果,系統(tǒng)使用M/T法[7]對(duì)速度數(shù)據(jù)進(jìn)行測(cè)量,M/T 法的計(jì)算公式如式(8)所示:

式(8)中f 為基準(zhǔn)時(shí)鐘頻率;P 為光電編碼器每轉(zhuǎn)一周產(chǎn)生的脈沖個(gè)數(shù);M1 和M2 分別是在相同的時(shí)間內(nèi)對(duì)編碼器脈沖和基準(zhǔn)時(shí)鐘脈沖進(jìn)行計(jì)數(shù)的計(jì)數(shù)值。

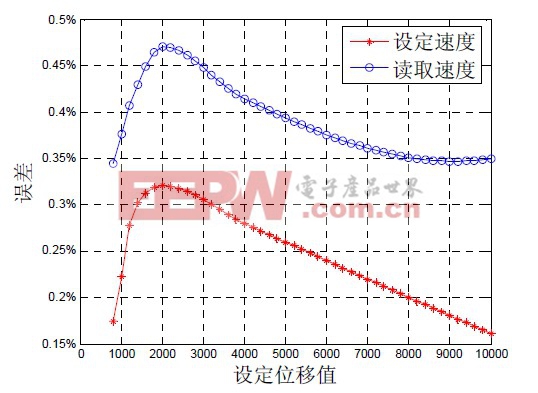

在電機(jī)空載時(shí)進(jìn)行了100 次試驗(yàn),圖8 所示為在實(shí)驗(yàn)室中測(cè)定的電機(jī)空載時(shí)的速度測(cè)試結(jié)果,各個(gè)參數(shù)值均是取100 次實(shí)驗(yàn)數(shù)據(jù)的平均值。圖8 中設(shè)定速度值對(duì)應(yīng)程序運(yùn)行時(shí)在脈沖發(fā)生器中設(shè)定的分頻系數(shù),驅(qū)動(dòng)器顯示電機(jī)轉(zhuǎn)速對(duì)應(yīng)設(shè)定速度時(shí)對(duì)應(yīng)的誤差,使用M/T 測(cè)得的轉(zhuǎn)速對(duì)應(yīng)讀取速度時(shí)對(duì)應(yīng)的誤差。

圖8 電機(jī)空載時(shí)速度測(cè)試結(jié)果

6 結(jié)論

采用嵌入式方案設(shè)計(jì)的運(yùn)動(dòng)控制系統(tǒng)不管在體積、成本還是功能方面,較原有的工控機(jī)+板卡的結(jié)構(gòu)均有較大的優(yōu)勢(shì)。該系統(tǒng)突破了原有的工業(yè)CT 運(yùn)動(dòng)控制系統(tǒng)本身固有的一些缺點(diǎn),采用嵌入式的ARM+FPGA 解決方案進(jìn)行設(shè)計(jì),控制系統(tǒng)內(nèi)部采用基于單神經(jīng)元自適應(yīng)PID 控制器進(jìn)行設(shè)計(jì)。系統(tǒng)運(yùn)行結(jié)果證明方案的可行性。為今后進(jìn)一步研發(fā)擁有自主知識(shí)產(chǎn)權(quán)的基于嵌入式系統(tǒng)的多軸智能運(yùn)動(dòng)控制器做了基礎(chǔ)性的探索工作。

參考文獻(xiàn):

[1].AT91RM9200 datasheethttp://www.dzsc.com/datasheet/AT91RM9200+_143939.html.

[2].EP1C6Q240C8 datasheethttp://www.dzsc.com/datasheet/EP1C6Q240C8+_1135222.html.

[3].M1 datasheethttp://www.dzsc.com/datasheet/M1+_2039447.html.

[4].M2 datasheethttp://www.dzsc.com/datasheet/M2+_2039448.html.

pid控制器相關(guān)文章:pid控制器原理

評(píng)論