基于32位ARM和μC/OS-II的心電信號處理系統

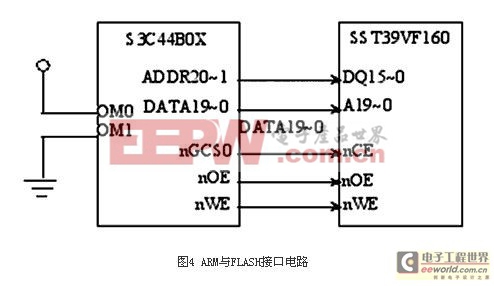

3 FLASH ROM電路設計

在心電信號處理系統中,S3C44B0X是硬件部分的中央處理器,而實時操作系統μC/OS-II是硬件資源的調度中心,它就存放在Flash ROM中,在每次系統初始化之后,由S3C44B0X將其復制到SDRAM中后,再進行應用程序的執行。

在本系統中使用的是SST公司生產的容量為1M×16bit的多用途FLASH存儲器SST39VF160。ARM與FLASH接口電路如圖4所示。

當S3C44B0X復位時,它立即從0x00000000地址處開始取指令執行。因此,系統啟動代碼放在了地址0x00000000處,并把定位在0x00000000處的存儲器稱為BOOT ROM,在ARM系統中,通常都采用能夠快速讀取并方便重新寫入的Flash ROM作為BOOT ROM。處理器對Flash ROM的接口不需要任何軟件上的設置,在系統第一次上電時,CPU就可對Flash ROM進行讀取了。

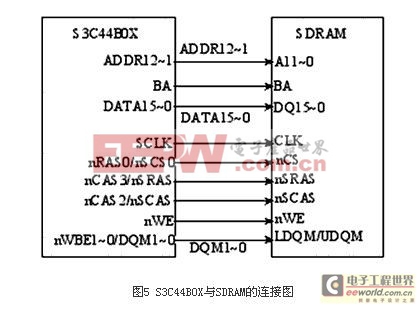

4 片外主存SDRAM的接口電路設計

在實時操作系統 μC/OS-II中,每個任務都有獨立的堆棧,并且是由連續的內存空間組成。在心電信號的傳輸過程中,還需要一個緩沖區進行數據的存儲,包括系統軟件運行所需要的堆棧等。這些都需要系統的主存來分配空間。

S3C44B0X內部只有8KB的緩存,沒有能用來運行程序和存放臨時數據的RAM,所以必須外接SDRAM作為片外主存。在本文中,采用的是ICS公司生產的容量為1Mb×16×4Bank的IS42S16400。

S3C44B0X與SDRAM的連接圖如圖5所示。

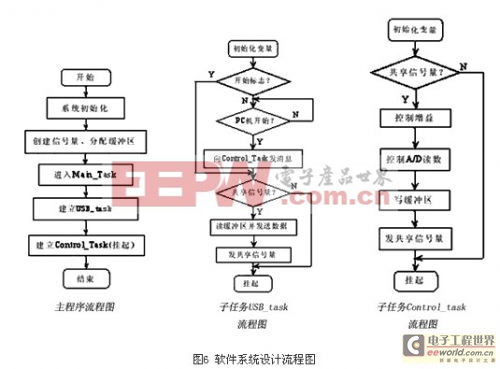

軟件系統設計

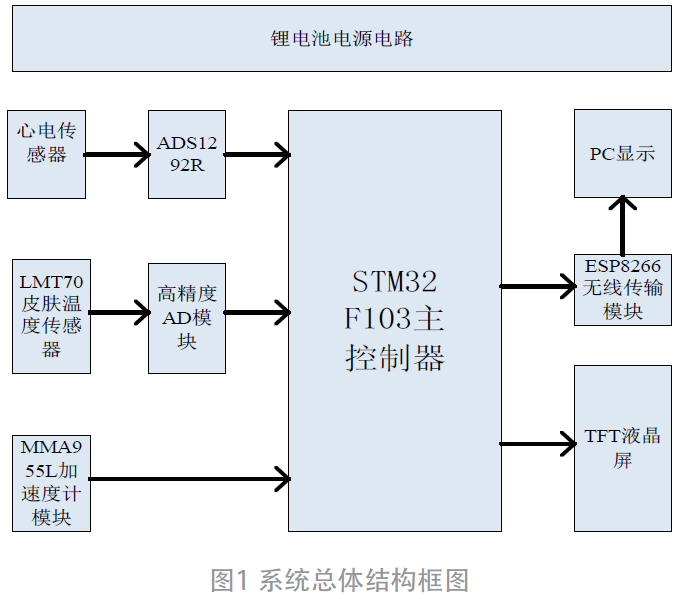

為了實現了對心電信號的量化和對數據的處理和傳輸,充分的利用μC/OS-II的實時性,并使軟件系統具有良好的可重用性,為以后對系統功能的擴展提供條件,本系統軟件設計如圖6所示。

抗干擾設計

心電信號傳輸到PC機端后,需要顯示到屏幕上,形成心電圖。在心電信號處理系統中采用的12導聯在屏幕上表現為12個心電波形,每一個波形都包含著特定的信息,但是要得到接近于理想的心電波形,就必須對信號進行預處理。

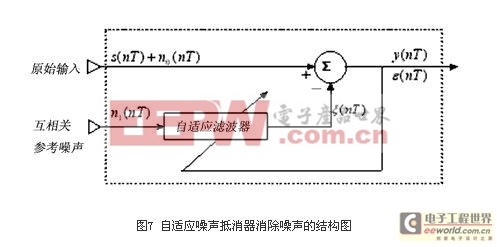

從測量技術上來說,心電信號屬于強噪聲背景下的低頻微弱信號,幅度為10μV~5mV,主要的頻率范圍為0.05~100Hz,因此,在心電信號的檢測、提取、放大及記錄過程中,有來自人體自身的干擾,如肌電干擾,也有來自外界的干擾如工頻干擾等。這些干擾使系統的信噪比下降,甚至會淹沒微弱的有效心電信號。因此,需要進行信號預處理以消除各種干擾。本文使用自適應噪聲抵消器來進行預處理,如圖7所示。

結束語

實驗表明,本文設計的基于ARM的心電信號處理系統,對信號的采集和處理部分采用的軟硬件模塊化設計,提高了心電信號檢測的精度。設計的以ARM處理器為核心的軟硬件系統和USB通信接口,提高了系統的穩定性和可靠性,達到了預期的技術指標,為設計新型的心電信號處理設備提供了理論基礎和依據,此系統也將為心臟病變的診斷發揮重要作用。

評論