為網絡、通信和高端計算系統中的分布式供電架構選擇芯片組

簡介

本文引用地址:http://www.104case.com/article/21525.htm網絡和通信設備的發展趨勢持續促進對于更多高級npu和asic的需求。在穿過骨干網或者從一個通信設備傳到另一個時,由于需要增長帶寬并對信息進行更復雜的分析,這就促進了更強大處理資源的使用。因為這些處理器能更好的處理這些任務,它們的功率要求也變得更加復雜。而處理器復雜程度的增長對功率要求更高。傳統系統功率架構僅提供幾個電壓及功率等級,但是這些架構已不能達到增長的系統要求。各種電源系統架構均衡功效、成本和復雜性。目前趨向于雙級架構。

在 網絡和通信系統中的電源架構(包括電信系統),具有來自容變彈性ac/dc整流器模塊48v額定輸入。各種系統將在額定電源電壓的上下浮動范圍內操作。例如,一個通用的電信系統輸入電壓范圍可能是36v到75v,而符合歐洲電信標準化協會(etsi)規范的系統將把范圍縮小到36v到60v。與這些不可調節的額定電源不同,一些系統是由可調節的48v總線操作的,其典型的總線電 源供 應范圍是 10%。電源架構必須以最大的電效率、最小的空間、最優化的成本將這個輸入電壓輸送到pol轉換器。

傳統分布穿過電路板電源的方法為下面兩個基本配置方案中的一個(圖1)。第一個方案。轉換器將輸出電壓從48v轉到3.3v,然后再通過幾個必備的pol轉換器將3.3v轉到所需的pol電壓。從傳統上來說,在電路板上,3.3v干線最需要電源,所以設計者選擇3.3v總線,以取得單級交換,從而消除功率損耗。另一個配置方案,適用于更高功率的電路板,它將輸出電壓從48v轉換到所謂的中級總線電壓(一般為12v),再將12v總線電壓轉換成pol電壓。

每個dpa都有其優點和缺點。當在電路板上有一個需要3.3v工作電壓的主負載、或整個電路板上覆蓋多個3.3v負載時,設計者通常會采用3.3v總線dpa。設計者通常這樣設計,以使電路板上的交換總額最小化,從而在最需電源端優化效率。然而,一個3.3v-總線-dpa系統要求對產生其它工作電壓的每個pol轉換器要進行偏壓供應。

另一個問題是3.3v的輸出需要一個串聯順序fet,因為隔離的轉換器通常缺少對于輸出速率的控制。串聯順序fet只有在啟動和斷電時才有用;在其它時候,dc-loss高架會影響效率、增加部件并提高費用。而且,由于操作電壓持續下降,支配分線很可能移向2.5v。對于同樣的主板電源,主板電流增長了32%,配電損耗增長了大約74%。

3.3v主線必須要產生電路板上所有其它操作電壓。可以存在幾個額外輸出電壓,每個電壓的輸出都可以使用高頻轉換dc/dc pol轉換器。pol轉換器的高頻轉換可以將噪波反向注入到3.3v輸入線,而且由于這個線直接供應負載,電源架構要求進行大量的過濾以保護3.3v 負載。3.3v總線也為asic提供動力,asic對于噪波非常敏感而且可以承受因過濾不足而產生的損壞--但這不是一個最佳選擇,因為asic的成本很高。

當 所有板上功率很高又沒有負載電壓來支配整個電路板時,設計者典型地采用一個12v的中線dpa。通過這種方法,因為對于給定的電流水平來說電流很低,所以分流損失很低。對于這種架構,pol轉換器產生了所有操作電壓。使用一個12v dpa來簡化pol轉換器。串聯順序fet也能在pol轉換器上控制啟動和斷電,盡管大多數可用pol轉換器可以直接控制這項功能。

今 天的12v輸出模塊是提供受控輸出的典型全性能程序塊。12v程序塊內的反饋通過光耦合器為轉換器的初級端提供一個符號反饋。具有高rm電流的12v程序塊,相對無效。它們要求24v到100v電壓的二級端fet,如果平均輸出電壓很低,就可能使用較低壓fet,二級端fet一般來講具有高于需要的接通電阻。因為模塊有大量組件,所以全控制程序塊都很浪費而且大于指定輸出功率。一個主板更加有效分配兩級功率的方法是建立一個處于3.3v到12v的中間非調節電壓。(圖 2)

新的pol轉換器可接受一個廣泛的輸入電壓范圍,這就意味著設計者可以利用產生中間總線電壓的單獨轉換級來采取一個更簡單的方法。根據輸出功率等級,pol轉換器的最佳輸入電壓在6v到12v之間。結果是獲得了占有少量空間并具有很少組件的高效、獨立轉換器。全功能程序塊,能在不增加整體設計復雜性的基礎上,使用50個或更多的組件。輸出電壓調節的移除為顯著減少模塊組件數提供了機會。一個不可調dc-總線轉換器使用一個單獨的轉換器,它處于固定的工作循環中,可以允許簡單、自行驅動的二級同步整流開關,達到最大化電源轉換效率、最小化輸入和輸出過濾并提高可靠性。

板上雙級電源轉換器

非調節dc-主線轉換器很快成為最受歡迎的能將48v輸入電壓轉換到中間主線、然后供應給pol的方法。一個具有開路、固定50%工作循環特征的簡易獨立轉換器能提供一個中間主線電壓,這個電壓由輸入電壓、初始端拓樸(半橋或全橋)和變壓器轉換率構成。

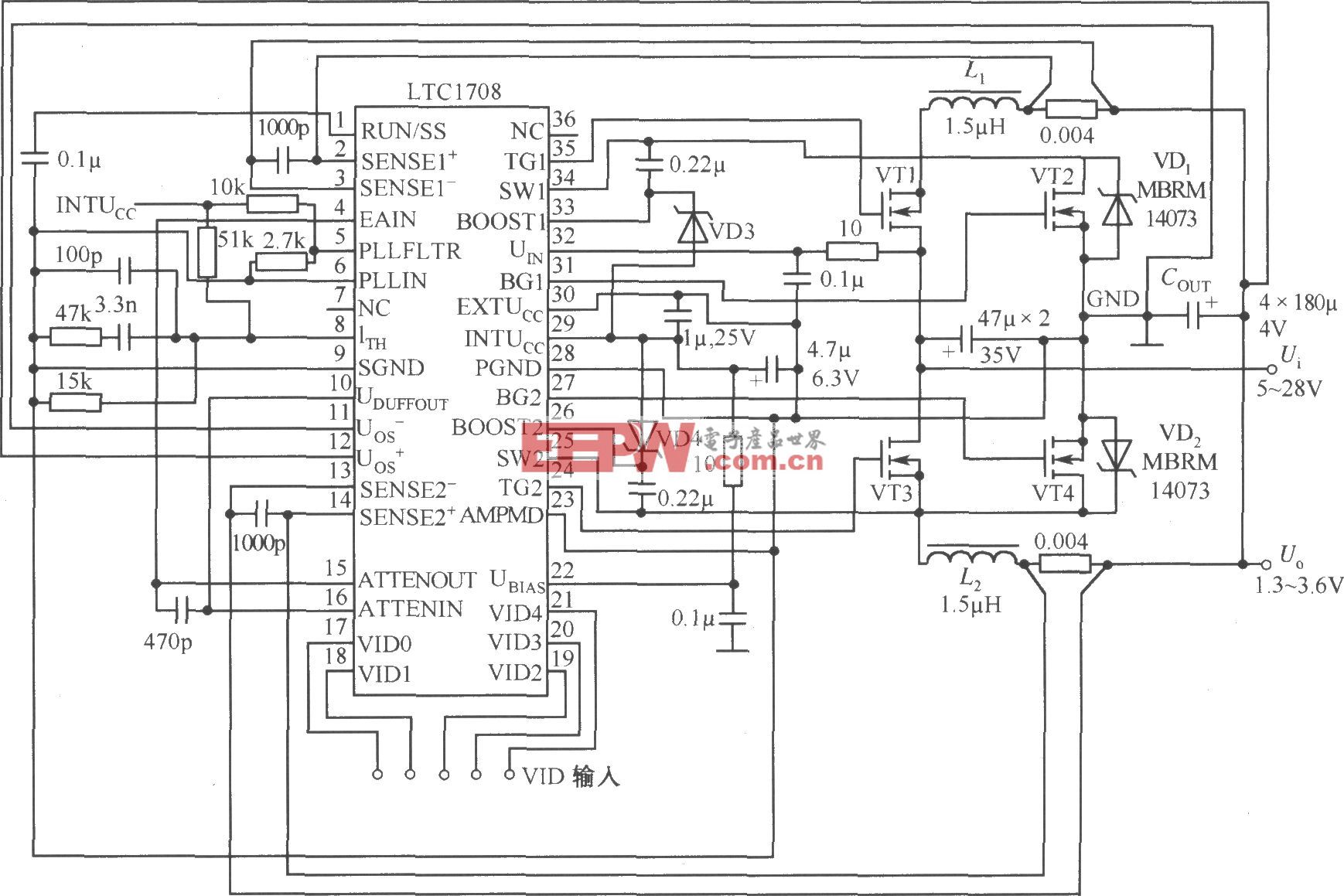

根據系統電源等級、pol轉換器配電頻率和配 電功耗計算,多數設計者在6到12v的范圍內設置額定主線電壓。dc-主線拓樸提供了在最小空間內的最大效率以達到用最較少的組件實現最好的電源密度、減少總成本。拓樸也要求最小的輸入和輸出過濾--又是一項 成本節省。這種方法也極大簡化了電源架構中的控制、監測 、同 步化和定序。圖3展示了dc-主線轉換器設計,這個設計應用了幾個能達到這種性能的創新技術。

國際整流器公司開發了包括自激振蕩驅動器和匹配電源mosfet的芯片集。ir2085s 和ir2086s高速、半橋和全橋驅動器,在48v雙級電路板電源分布系統中,分別服務于非調節、單獨dc-主線轉換器。這些控制器通常具有高性能、高簡化而且成本低。它們使用100v、1a的驅動器將50%工作循環振蕩器與用于半橋ir2085s

的so-8封裝和用于全橋ir2086s的so-16相結合。設計者能夠從外部調節ic頻率和停歇時間,以滿足多種應用要求。器件也提供了啟動和電源限制功能。一個內部軟啟動特點限定了啟動期間的瞬間起峰電流,在50%的工作循環中逐漸增長電流。軟啟動可持續大約2000脈沖的門驅動信號。國際整流器公司的48-v

dc-總線參考設計,利用低負荷、強電子熱、初級端、mosfet和低電子熱、二級端的新ic控制器全橋版本,能在小于程序塊八分之一空間的范圍內,達到97%的效率。

這個效率比常規的、全控制、板上電源轉換器要高出3-5%。

在初級端,ir2085s 驅動兩個 irf6646 fet,即下一代的低負載80v directfet。對于36v到75v的輸入電壓,設計者能將fet轉換成100v

irf6644。器件能通過一個用于啟動的小線性控制器和穩定狀態下的變壓器來達到其初級端的偏流。在二極端上的兩個30v、n-channel

irf6635 directfet在自動同步整流器拓樸中進行操作。

directfet-半導體封裝除去了mosfet封裝阻抗,這就降低了總阻抗從而提高了主要效率。對于頂層冷卻,directfet封裝也允許一個典型的1℃/w結一板熱阻及最大化的1.4℃/w結一殼熱阻。

一個220w dc-主線轉換器能達到2.05 x 0.85英寸--比八分之一程序塊的行業標準小了15%。對于四分之一dc-主線轉換器設計可以節省近50%的空間。在這個小覆蓋區內220v轉換器能獲得96%的效率(圖6)。

220w設計使用了一個220 khz的初級端配電頻率以使其性能最優化:高配電頻率減少了輸出電壓波和變壓器通壓密度,可以使用更小的磁性組件。同樣,一個變壓器更小的核會產生更小的功耗。然而,高配電頻率增加了初級和二級配電功耗并產生低的總電路效率。

用于高功率應用的dc-總線轉換器可以使用ir2086s高速、100v、全橋驅動和初級和二級端directfet,用小于八分之一程序塊空間達到的97%效率,在9.6v的電壓下提供高達330w的功率。

非獨立pol轉換器

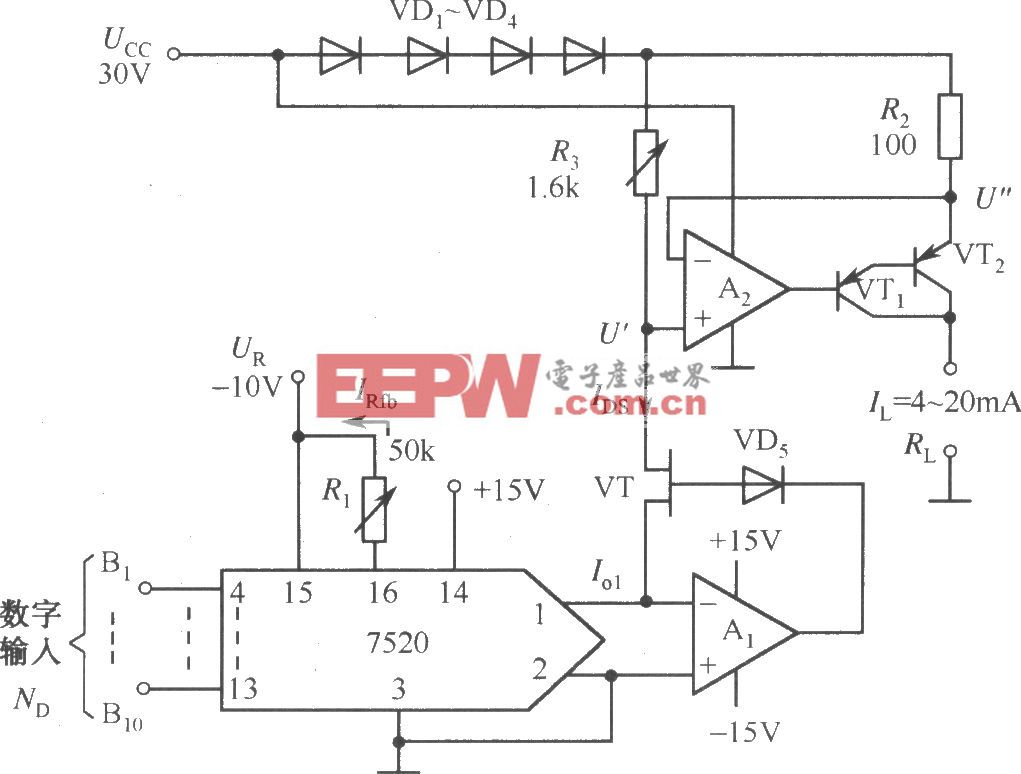

d c-總線轉換器在兩級dpa中屬于前端級。當設計者在設計第二級、非獨立pol轉換器時產生了許多獨特思考。當主要考慮電路板空間和設計復雜性時,嵌入式程序塊設計在整體模塊和全離散設計上具有很多優勢。例如:國際整流器公司的ipowir的程序塊為mcm(多芯模塊),包含了達到高效率、雙相位同步降壓轉換器。其中包括振蕩器、加速器、誤差信號放大器,pwm比較器,控制pet,同步fet等所有器件,但是有一些是為完成pol轉換器的被動需要。程序塊執行像超電壓保護、超電流保護和超溫保護這樣的功能。程序塊也 提供內部控制和同步fet間歇控制。除了減少90%pol轉換器部件數,ipowir程序塊能通過減少挑戰性電路板設計靈敏度來明顯壓縮設計時間并減少風險。通過在ipowir程序塊 周圍使用幾個外部組件,一個設計者可以快速、簡單的建立高性能、雙相位、雙輸出和同步buck轉換器,以滿足幾個負載電壓要求。(圖4)。相對于備選同等離散設計,程序塊方法除了簡化了設計者 的工作,也極大的減少了設計時間并節省了pc-電路板上50%的空間。設計者從而得到一個經測試、有保證的器件,這個器件一般來講沒有離散設計復雜的布局問題,具有眾所周知的最大功耗。這個器件能為其它負載電壓進行簡單布局的靈活性,同時,也產生高轉換效率。

與輸入電壓相比,pol轉換器通常有高輸入電壓。典型的工作循環范圍為10%到20%,在同步buck電流中相當于高端mosfet的及時電壓。 高端mosfet或者控制fet采用轉換模式(圖4)手工操作。相應的mosfet的簡化功耗公式是:

在控制fet中 引起電源分散的主要因素是傳導功耗,轉換功耗,門驅動功耗,其中最主要的是轉換功耗。為了使轉換功耗最小化,設計者應該選擇低負載mosfet并考慮與轉換相關的電壓,或者后門檻電壓,負載項目包括qgs2 和qgd。moseft僅在門驅動電壓超過門檻電壓后才開始實行,所以在門驅動電壓通過門檻電壓時沒有功耗。一旦開始實行mosfet,功率就開始分散,后門檻電壓負載越低,轉換負載也越低。輸入電壓和配電頻率也會形成轉換功耗。降低輸入電壓和減少配電頻率也會減少整體功耗。然而,在高功率應用中,一個較低的輸入電壓產生了換位。由于輸入電流成比增加,整體的分流功耗也會增加。同時,根據感應器的尺寸或者轉換器所用到的過濾電容器的數量,減少配電頻率也能顯著的增加轉換器的尺寸。

基于高端系統在高頻度下操作的事實,控制fet的總體門負載應該適當的降低以減少門驅動功耗。低負載控制fet能減少開關節點上的尖峰信號(圖6)。尖峰信號能開啟同步fet,引起貫通電流,這會降低可靠性并引起內電路故障。同步的fet能在下列條件下進行保護:如果fet的負載率 與qgs1的比率 小于1.4,門電壓尖峰信號將不會超過極限電壓。

在高電流系統中,控制fet必須也顯示低阻抗以減 少傳導功耗,這個功耗與電流平方成比例。對于這些系統,優化控制fet選項的指標系數結合了門負載和阻抗。選擇一個低端mosfet還是合成的fet,要取決于不同的分析。相應的這個器件的簡化功耗公式是:

同步fet沒有顯示出轉換功耗組件,因為它們是在零伏特模式下操作的。實行前,在電路中產生了一段間歇時間,在這段期間感應器電流在同步fet的主體二級管間循環流動。與轉換器的操作電壓相比,主體二極管的正向電壓接近于零,因此,當同步fet開啟時,功率并不同時分散。pol轉換器的10-20%的工作循環在同步fet上產生了80-90%的有效工作循環。由于fet大部分的時間都用于傳導模式上,轉換器的設計者選擇主要器件的標準在阻抗上。

評論