基于FPGA的通用位同步器設計方案(一)

該同步器工作過程如下:外部控制器根據基帶碼元速率設置相應參數,通過外部控制器接口將控制、地址和數據信號分別送往分頻器、環路濾波器和內部控制器。時鐘電路分別提供采樣時鐘和FPGA 時鐘,FPGA工作時鐘在片內通過分頻器產生所需頻率的時鐘,供FPGA 各模塊使用。輸入連續時間信號x(t) 經由獨立時鐘控制的ADC 進行采樣,轉換為8 位數字信號送至FPGA 內,符號化后變為有符號數字序列,送入內插濾波器模塊。內插濾波器根據輸入信號的采樣值和內部控制器給出的參數μk,在每個插值時刻kTi 計算出最佳判決點的內插值y(kTi)。定時誤差檢測計算出誤差μτ (n),輸出至環路濾波器。環路濾波器依據當前的參數設定,濾除噪聲并將誤差信息送給內部控制器。內部控制器以NCO為核心,根據處理后的誤差信息和設定的頻率字參數調整插值時刻kTi,使之盡可能接近最佳判決時刻,并輸出位同步脈沖BS,同時計算出誤差間隔μk 送給內插濾波器,進行內插值計算,最終完成定時信息的恢復。

2 FPGA設計

2.1 整體結構設計

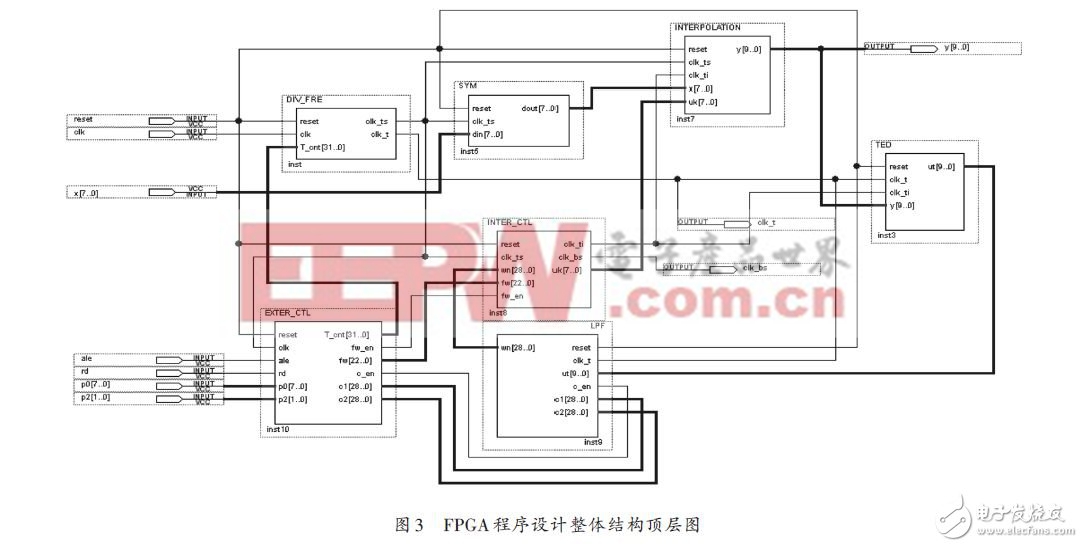

根據圖2的算法結構,FPGA設計采用模塊化方式,整體結構的頂層圖如圖3所示。

從圖3可以看到,該設計包含分頻器(DIV_FRE)、符號化(SYM)、內插濾波器(INTERPOLATION)、定時誤差檢測(TED)、環路濾波器(LPF)、內部控制器(INTER_CTL)和外部控制器接口的時序電路(EXTER_CTL)共7個模塊。其中,分頻器由片外晶振提供時鐘輸入,分頻后為片內其他模塊提供相應時鐘。其中碼元時鐘的分頻系數可由外部控制器通過接口進行設置。符號化是將A/D采樣產生的無符號數轉換為有符號數,以便后續模塊進行帶符號的運算。

外部控制器接口的時序電路將外部控制器送來的控制信號(ALE和RD)、地址信號(P2.0、P2.1)和數據信號(P0口)、轉換為FPGA 內分頻器、環路濾波器和NCO的使能信號和參數,實現對位同步器各參數的設置。

分頻器、符號化和外部控制器接口模塊實現較為簡單,不再贅述。而內插濾波器、定時誤差檢測、環路濾波器和內部控制器的實現較為復雜,且本設計通過采用相應算法和改進結構,實現了位同步器的通用性。本文將詳細闡述這些模塊的設計。

2.2 模塊詳細設計

2.2.1 內插濾波器設計

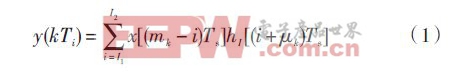

內插濾波器是完成算法的核心,它根據內插參數實時計算最佳判決點的內插值,即:

式中:mk 為內插濾波器基點索引,決定輸入序列中哪些采樣點參與運算,它由插值時刻kTi 確定;μk 為誤差間隔,決定了內插濾波器的沖激響應系數[1].kTi 和μk 的信息由內部控制器反饋回來。

本設計的內插濾波器采用基于4 點分段拋物線多項式的Farrow結構實現。將式(1)變換為拉格朗日多項式,即令:

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理

評論