基于FPGA的通用位同步器設(shè)計(jì)方案(一)

本文主要是先闡述傳統(tǒng)Gardner算法的原理,然后給出改進(jìn)后的設(shè)計(jì)和FPGA實(shí)現(xiàn)方法,最后對(duì)結(jié)果進(jìn)行仿真和分析,證明該設(shè)計(jì)方案的正確、可行性。

0 引言

數(shù)字通信中,位同步性能直接影響接收機(jī)的好壞,是通信技術(shù)研究的重點(diǎn)和熱點(diǎn)問(wèn)題。通信系統(tǒng)中,接收端產(chǎn)生與發(fā)送基帶信號(hào)速率相同,相位與最佳判決時(shí)刻一致的定時(shí)脈沖序列,該過(guò)程即稱為位同步。常見(jiàn)的位同步方法包括濾波法和鑒相法。濾波法對(duì)接收波形進(jìn)行變換,使之含有位同步信息,再通過(guò)窄帶濾波器濾出,缺點(diǎn)是只適用于窄帶信號(hào)。最為常用的位同步方法是鑒相法,包括鎖相法和內(nèi)插法兩種。鎖相法采用傳統(tǒng)鎖相環(huán),需要不斷調(diào)整本地時(shí)鐘的頻率和相位,不適合寬速率范圍的基帶碼元同步。而內(nèi)插法則利用數(shù)字信號(hào)的內(nèi)插原理,通過(guò)計(jì)算直接得到最佳判決點(diǎn)的值和相位。

Gardner算法即是基于內(nèi)插法的原理,通過(guò)定時(shí)環(huán)路調(diào)整內(nèi)插計(jì)算的參數(shù),從而跟蹤和鎖定位同步信號(hào),該算法的優(yōu)點(diǎn)在于不需要改變本地采樣時(shí)鐘,可以適應(yīng)較寬速率范圍內(nèi)的基帶信號(hào),因而具有傳統(tǒng)方法不可替代的優(yōu)勢(shì)。Gardner算法的實(shí)現(xiàn)方法,為算法的應(yīng)用提供了基礎(chǔ)。Farrow結(jié)構(gòu)非常適合實(shí)現(xiàn)Gardner算法的核心,即內(nèi)插濾波器部分,其優(yōu)點(diǎn)是資源占用較少,且濾波器系數(shù)實(shí)時(shí)計(jì)算,便于內(nèi)插參數(shù)調(diào)整。定時(shí)誤差檢測(cè),但在定時(shí)誤差檢測(cè)時(shí)需要信號(hào)中存在判定信息,并且對(duì)載波相位偏差敏感。不足進(jìn)行了改進(jìn),提出了GA-TED(Gardner Timing Error Detection)算法,其優(yōu)點(diǎn)是不需要預(yù)知判定信息,且獨(dú)立于載波同步,并且適合FPGA 實(shí)現(xiàn)。改進(jìn)的Gardner 算法,并將其應(yīng)用于M-PSK 系統(tǒng)。提高了Gardner 算法的抗自噪聲能力,即降低了對(duì)本地時(shí)鐘的要求。

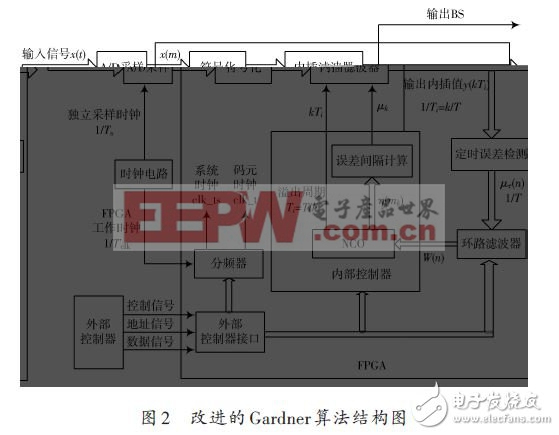

本文基于FPGA 平臺(tái)并采用Gardner 算法設(shè)計(jì),其中,內(nèi)插濾波器采用Farrow 結(jié)構(gòu),定時(shí)誤差檢測(cè)采用GA-TED算法。同時(shí)對(duì)傳統(tǒng)Gardner算法結(jié)構(gòu)進(jìn)行了改進(jìn),使環(huán)路濾波器和NCO的參數(shù)可由外部控制器設(shè)置,以適應(yīng)不同速率的基帶碼元,實(shí)現(xiàn)通用的位同步器的設(shè)計(jì)方案。此外,本設(shè)計(jì)方案還對(duì)FPGA 代碼進(jìn)行了優(yōu)化,節(jié)省了大量硬件資源。最后進(jìn)行了仿真和分析,給出了仿真結(jié)果,證實(shí)了該方案的可行性。

1 傳統(tǒng)Gardner 算法與改進(jìn)

1.1 傳統(tǒng)Gardner算法基本原理

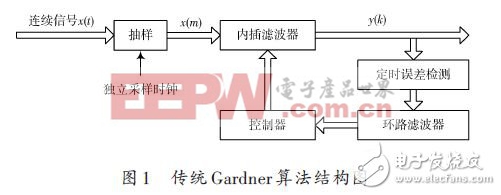

傳統(tǒng)Gardner算法結(jié)構(gòu)如圖1所示。

在圖1中,輸入的連續(xù)時(shí)間信號(hào)x(t) 碼元周期為T,頻帶受限。在滿足奈奎斯特定理的條件下,接收端采用獨(dú)立時(shí)鐘對(duì)x(t) 進(jìn)行采樣。內(nèi)插濾波器計(jì)算出內(nèi)插值y(k),送至定時(shí)環(huán)路進(jìn)行誤差反饋和參數(shù)調(diào)整,并與控制器輸出的位同步脈沖BS一起送往解調(diào)器的抽樣判決器。

定時(shí)環(huán)路包含定時(shí)誤差檢測(cè)、環(huán)路濾波器和控制器。定時(shí)誤差檢測(cè)提取插值時(shí)刻和最佳判決時(shí)刻的誤差;該誤差經(jīng)環(huán)路濾波器濾除高頻噪聲后送給控制器;控制器計(jì)算插值時(shí)刻(即為位同步信號(hào)的2倍頻)和誤差間隔。插值時(shí)刻和誤差間隔用于調(diào)整內(nèi)插濾波器的系數(shù),使插值時(shí)刻盡可能與最佳判決點(diǎn)同相,最終實(shí)現(xiàn)位同步信號(hào)的提取。

1.2 改進(jìn)的Gardner算法結(jié)構(gòu)

從上節(jié)可以看出,傳統(tǒng)Gardner算法無(wú)法滿足較寬速率范圍基帶信號(hào)的位同步要求。為實(shí)現(xiàn)該要求,本設(shè)計(jì)在FPGA 平臺(tái)的基礎(chǔ)上,對(duì)算法實(shí)現(xiàn)結(jié)構(gòu)進(jìn)行了改進(jìn),改進(jìn)結(jié)構(gòu)如圖2所示。

圖2中,內(nèi)插濾波器采用Farrow結(jié)構(gòu)的FIR 濾波器實(shí)現(xiàn),濾波器

濾波器相關(guān)文章:濾波器原理

fpga相關(guān)文章:fpga是什么

濾波器相關(guān)文章:濾波器原理

電源濾波器相關(guān)文章:電源濾波器原理

數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理

評(píng)論