用先進的SPICE模型模擬MOSFET電流-電壓特性

在本文中,我們使用90nm CMOS的SPICE模型來繪制NMOS晶體管的關鍵電學關系。

本文引用地址:http://www.104case.com/article/202407/460569.htm在前一篇文章中,我解釋了如何獲得集成電路MOSFET的高級SPICE模型,并將其納入LTspice仿真中。然后,我們使用這個模型來研究NMOS晶體管的閾值電壓。在本文中,我們將使用相同的模型來生成直觀地傳達晶體管電氣行為的圖。

繪制漏極電流與漏極電壓

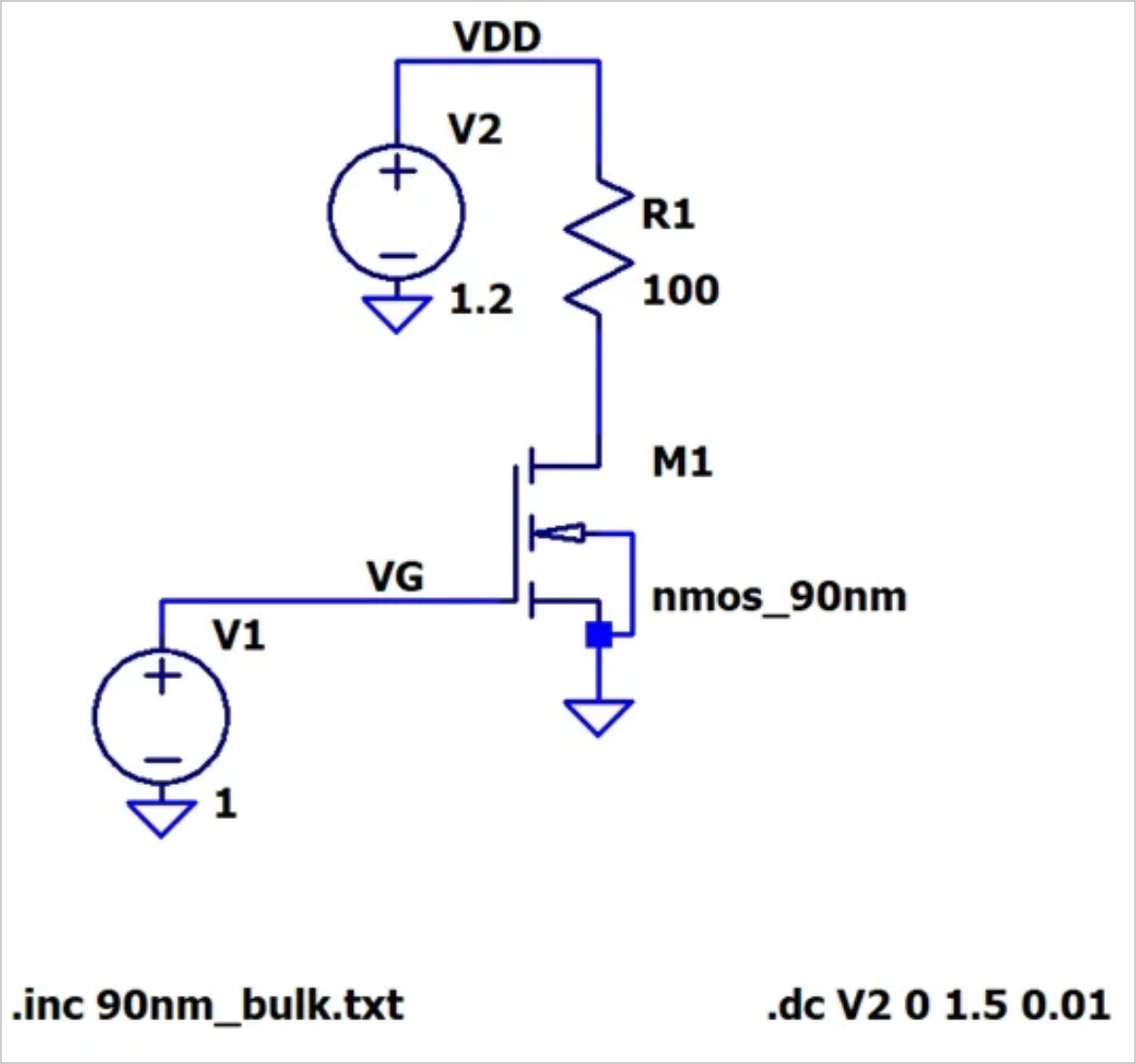

我們將從生成漏極電流(ID)與漏極-源極電壓(VDS)的基本圖開始。為此,我們將柵極電壓設置為遠高于閾值電壓的固定值,然后執行直流掃描模擬,其中VDD的值逐漸增加。圖1顯示了我們將要使用的示意圖。

用于產生漏極電流對漏極電壓曲線的LTspice NMOS示意圖。

圖1。基本NMOS晶體管的LTspice示意圖。我們將使用它來生成漏極電流與漏極電壓的曲線。

1V的柵極-源極電壓(VGS)遠遠高于320 mV,這是我們在前一篇文章中通過模擬發現的閾值電壓。同時,圖1右下角的.dc模擬命令告訴LTspice做兩件事:

以0.01 V的增量將V2電源(VDD)從0 V增加到1.5 V。

使用此系列VDD值作為自變量。

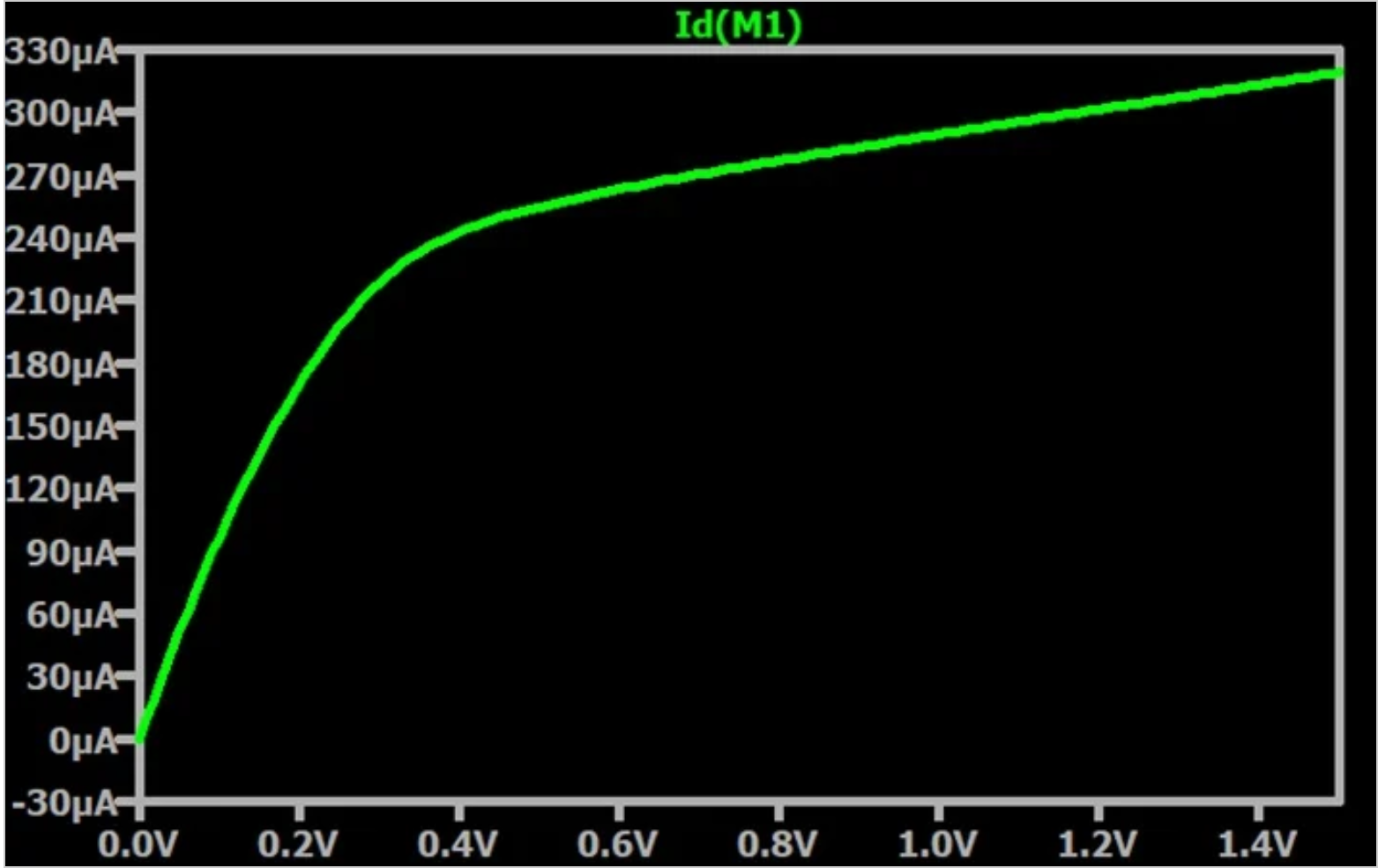

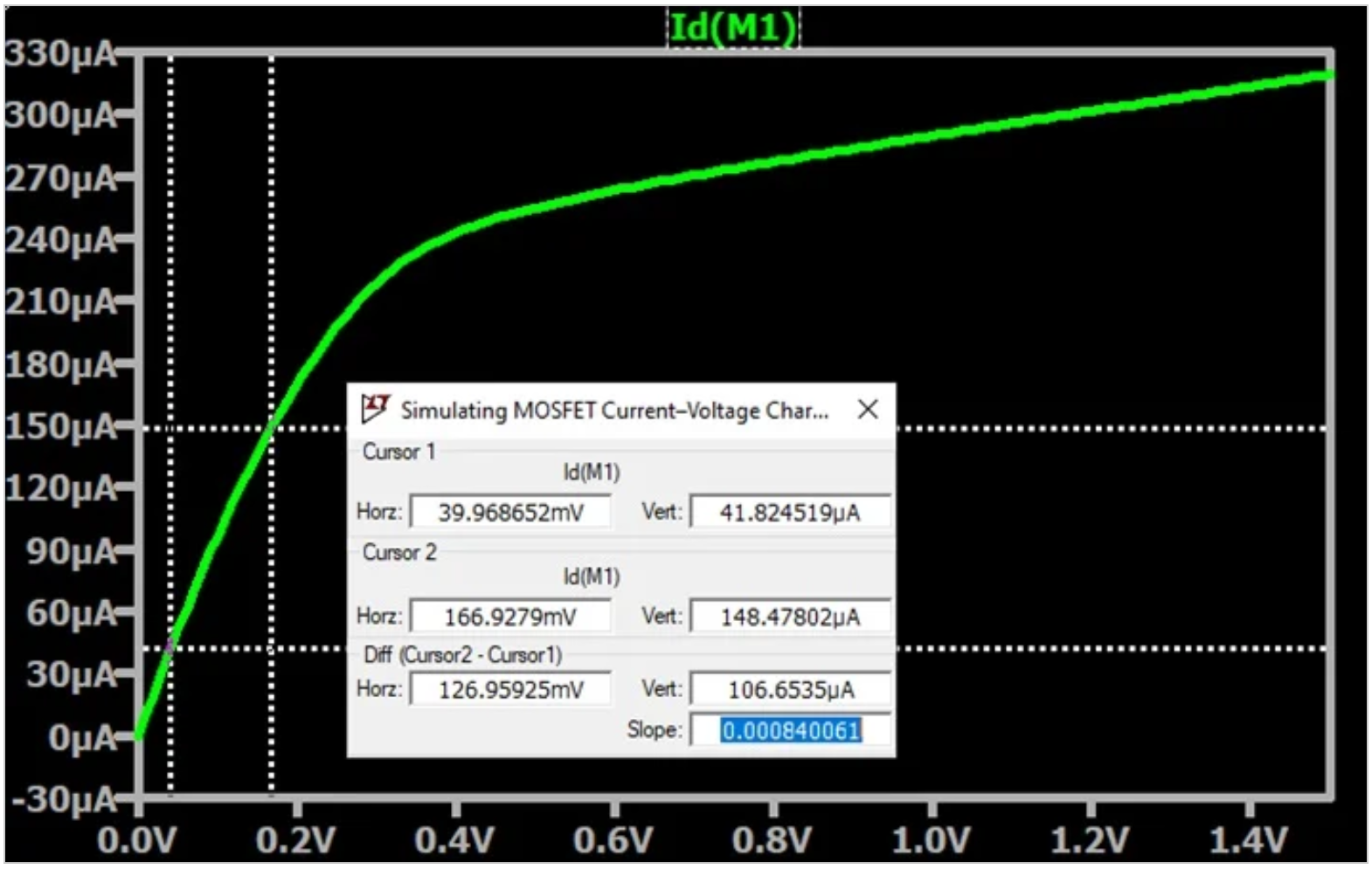

我們的模擬結果如圖2所示。

圖1中NMOS晶體管的漏極電流與漏極電壓。

圖2:我們的漏極電流與漏極-源極電壓的初始曲線圖。

柵極電壓足夠高以使能導通,因此一旦VDS增加到零以上,電流就開始流動。對于較低的漏極電壓,漏極電流響應于VDS的線性增加而線性增加。然而,漏極電流在大約0.4V處開始變平,并且此后增加得更慢。從曲線圖的較高斜率部分到較低斜率部分的這種轉變對應于從FET的線性區域到其飽和區域的轉變。

當漏極電壓較低時,柵極電壓打開從漏極延伸到源極的溝道,電流更自由地流過FET的溝道。隨著漏極電壓接近過驅動電壓,漏極處的溝道被夾斷,電流不再像以前那樣自由流動。過驅動電壓等于柵極電壓減去閾值電壓。

測量線性區域的電阻

線性區域中的NMOS表現得像電壓控制的電阻器。這就是這個區域的名字——當電流流過普通電阻時,電壓和電流之間的關系是線性的。如果我們觀察歐姆定律,這一點是顯而易見的:

如果我們用我們許多人在高中代數中使用的字母代替V、I和R,歐姆定律就變成了:

解釋

y、 縱軸,是電壓

x、 橫軸,是電流

m、 繪制線的斜率是阻力。

為了確定線性區域中NMOS晶體管的電阻,我們只需要找到m。由于我們在圖2中繪制了漏極電流和漏極電壓之間的關系,我們已經完成了一半。然而,我們在y軸上繪制電流,在x軸上繪制電壓——要使V=IR工作,電壓必須是y值,電流必須是x。m不是圖2中直線的斜率,而是斜率的倒數。

這只增加了一個額外的步驟。我們使用LTspice來找到斜率(圖3),然后取倒數。

光標框顯示漏極電流與漏極電壓曲線的斜率。

圖3。在FET的線性區域中找到漏極電流與漏極電壓曲線的斜率。

該線的斜率為0.00084。因此,總電阻為1/0.00084=1190Ω。該總電阻包括一個100Ω的漏極電阻器,使NMOS的溝道電阻等于1090Ω。

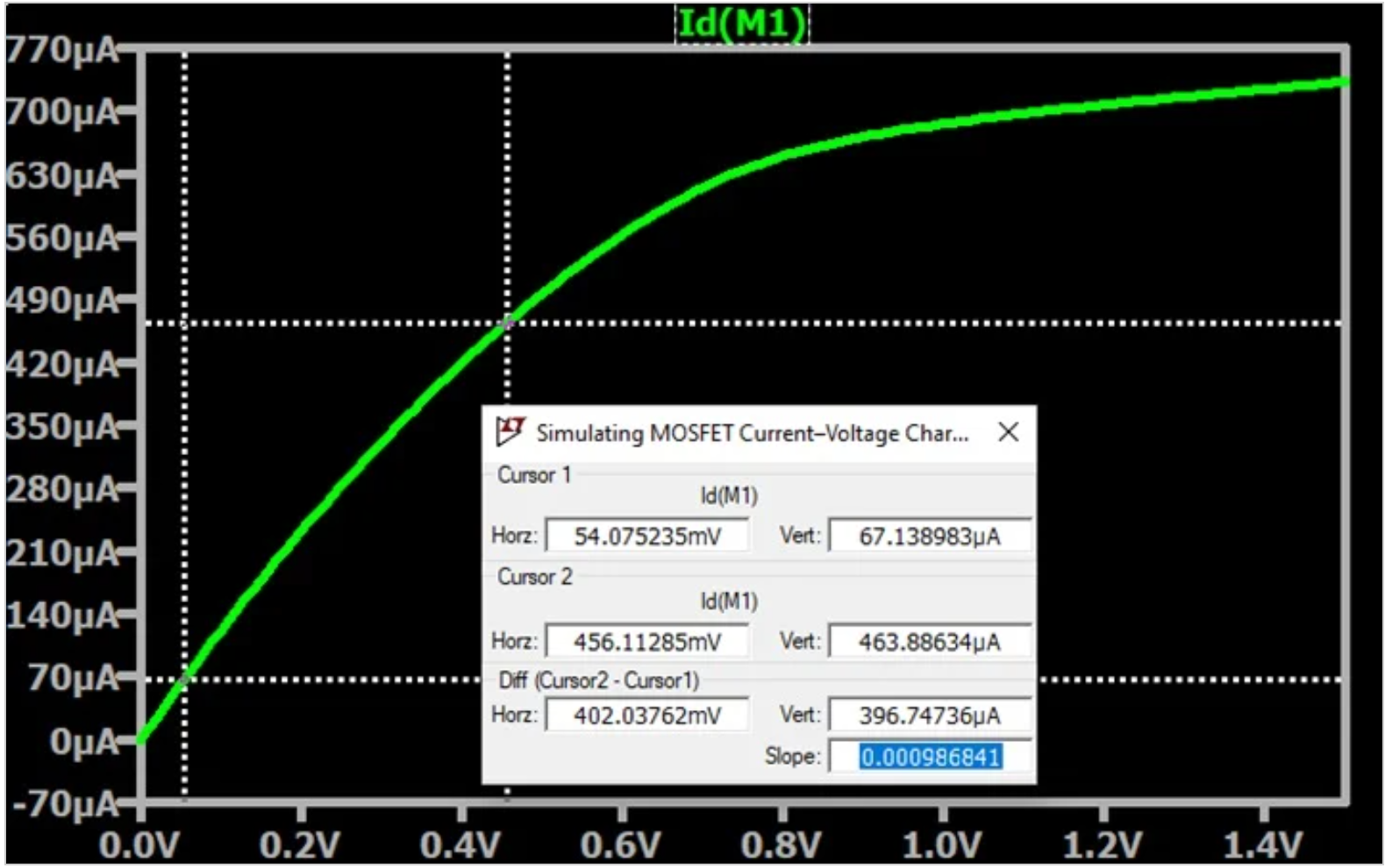

更高的柵極-源極電壓使溝道更導電,因此如果我們增加柵極電壓,我們可以預期該電阻會降低。圖4顯示了如果我將柵極電壓增加到2V會發生什么。

一旦柵極電壓增加,漏極電流對漏極電壓曲線的斜率。

圖4。一旦柵極電壓增加到2V,漏極電流對漏極電壓曲線的斜率。

當VGS=2 V時,斜率等于0.00099。取該值的倒數得出1010Ω。一旦我們減去100Ω的漏極電阻,FET在線性區域的溝道電阻為910Ω。這比我們之前的電阻值減少了180Ω,所以我們可以認為我們的預期得到了證實。

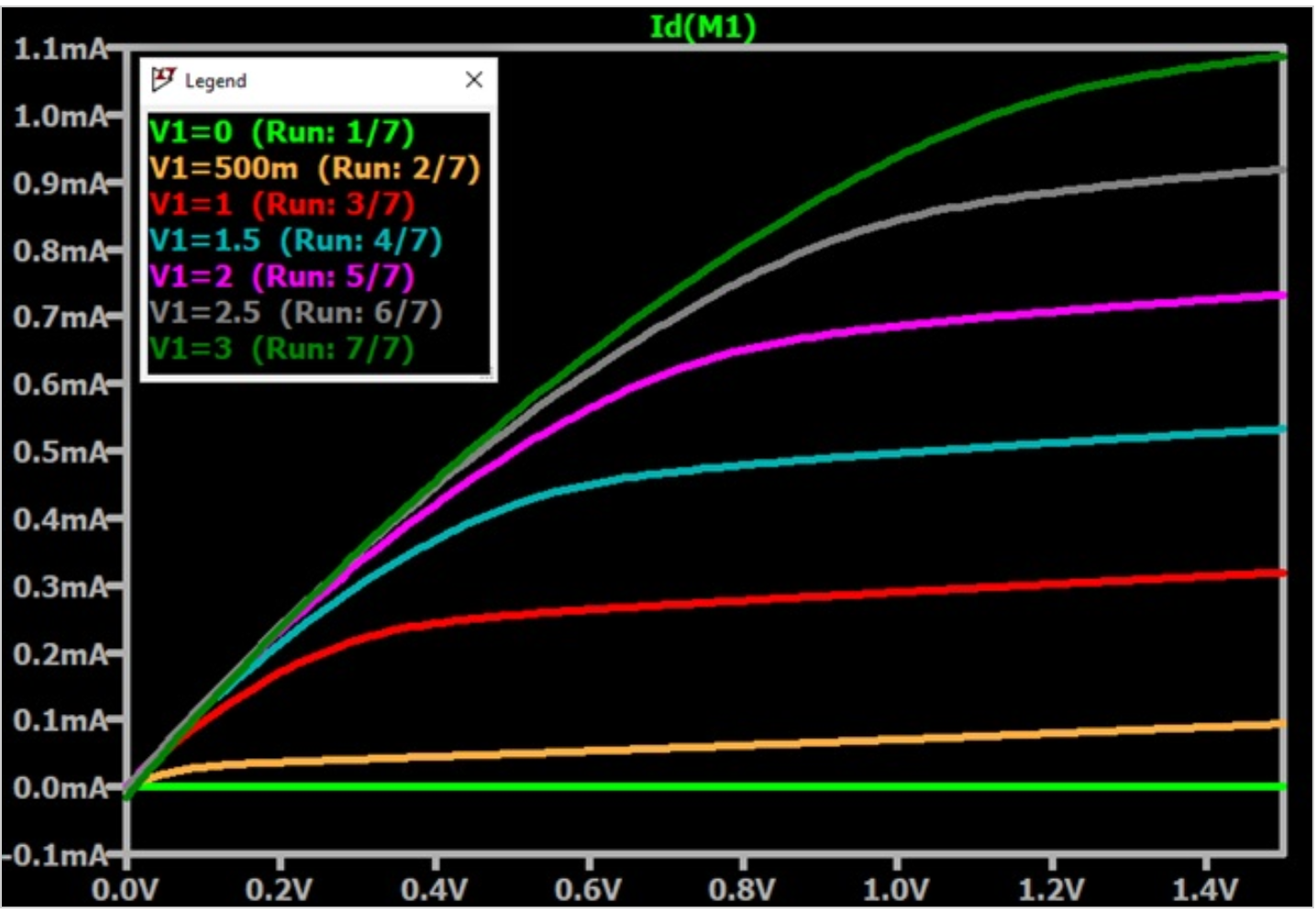

生成一組特征曲線

FET行為的討論通常伴隨著漏極電流對漏極電壓的圖,該圖包括多條曲線來表示不同柵極到源極電壓的結果。這允許單個繪圖來傳達關于柵極到源極電壓、漏極到源極的電壓和漏極電流之間的電關系的大量信息。

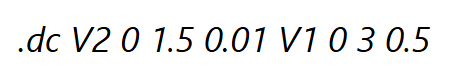

要在LTspice中生成這種類型的圖,我們只需要修改模擬命令,使其指定V2和V1(即柵極電壓)的掃描。新的模擬命令是:

V2掃描與以前相同,但我們添加了文本,告訴LTspice以0.5 V的增量將V1源從0 V增加到3 V。結果是圖5中的多色圖。

七個不同柵極電壓值的漏極電流與漏極電壓。

圖5。柵極電壓的七個不同值的漏極電流與漏極電壓。

要使繪圖顯示如圖5所示的圖例,只需執行以下步驟:

在繪圖窗口上單擊鼠標右鍵。

轉到“查看”。

選擇步驟圖例。

總結

SPICE模擬是了解更多MOSFET和研究細微電氣細節或復雜電路實現的好方法。預測技術模型網站上免費提供的高級模型使我們即使在使用現代集成電路中使用的MOSFET技術時也能保持模擬的準確性。

評論