使用先進的SPICE模型表征NMOS晶體管

為特定CMOS工藝節點設計的SPICE模型可以增強集成電路晶體管的模擬。了解在哪里可以找到這些模型以及如何使用它們。

我最近寫了一系列關于CMOS反相器功耗的文章。該系列中的模擬采用了LTspice庫中預加載的nmos4和pmos4模型。雖然這種方法完全適合這些文章,但如果我們的主要目標是準確模擬集成電路MOSFET的電學行為,那么結合一些外部SPICE模型是有意義的。

在本文中,我將介紹下載用于IC設計的高級SPICE模型并在LTspice原理圖中使用它們的過程。然后,我們將使用下載的模型對NMOS晶體管進行一些基本的電學表征。

尋找用于仿真的Spice模型

以前,我的免費MOSFET模型來源是預測技術模型(PTM)網站。不幸的是,URL不再處于活動狀態,但您仍然可以通過網站的存檔版本訪問模型。你也可以嘗試以下任何一種模型來源,盡管我還沒有使用過它們:

SkyWater與谷歌合作提供的130 nm CMOS模型,用于創建開源工藝設計套件(PDK)。

來自北卡羅來納州立大學的FreePDK。

在本文中,我們將使用PTM網站上的CMOS模型。你可以導航到我鏈接到上面的網站檔案,然后點擊“最新型號”來找到它。在那里,你會看到大量適用于不同CMOS工藝節點的SPICE型號,從180 nm一直到7 nm多柵極技術。

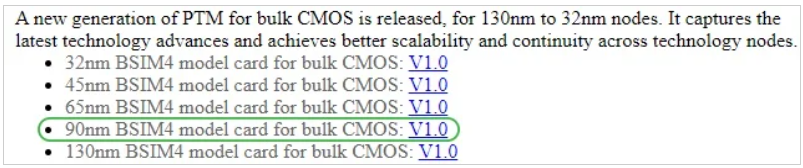

我們希望PTM型號標記為“90nm BSIM4大體積CMOS型號卡”。圖1顯示了最新型號頁面的相關部分,正確的型號用綠色圈出。

用于體CMOS的90nm BSIM4型號卡。

圖1。用于體CMOS的PTM 90 nm BSIM4型號卡。圖片由亞利桑那州立大學提供

將模型引入LTspice

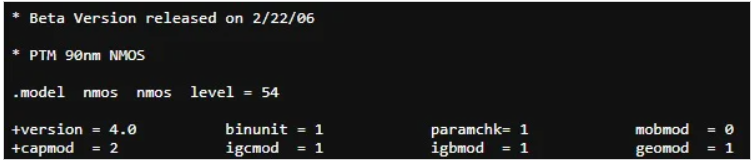

現在我們已經找到了我們的模型,我們需要將其添加到LTspice中。首先單擊模型名稱右側的鏈接文本。當您這樣做時,您將看到一頁包含大量SPICE參數的文本。圖2顯示了前幾行中的一小部分文本。

90 nm PTM型號的幾行文字。

圖2:90 nm PTM型號的幾行文字。圖片由亞利桑那州立大學提供

復制頁面上顯示的所有內容并將其粘貼到文本文件中。完成后,將新的文本文件保存在保存LTspice原理圖文件的同一目錄中。

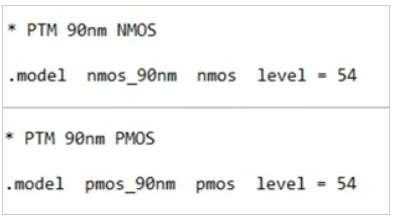

我將我的文本文件命名為90nm_bulk.txt(術語“bulk”指的是使用標準硅片制造的CMOS電路)。.model語句后面的單詞是我們在LTspice中用來引用此模型的名稱。我喜歡使用比“nmos”或“pmos”更具體的東西,所以我將模型名稱(圖3)更改為nmos_90nm和pmos_90nm。

NMOS和PMOS型號名稱。

圖3。NMOS和PMOS型號名稱。圖片由Robert Keim提供

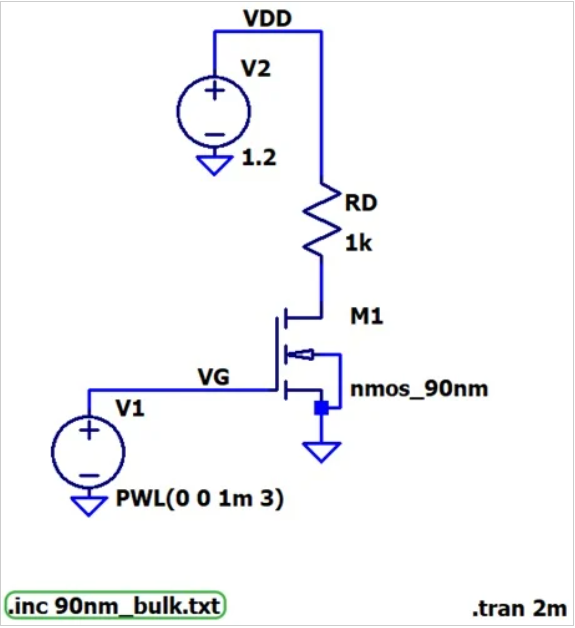

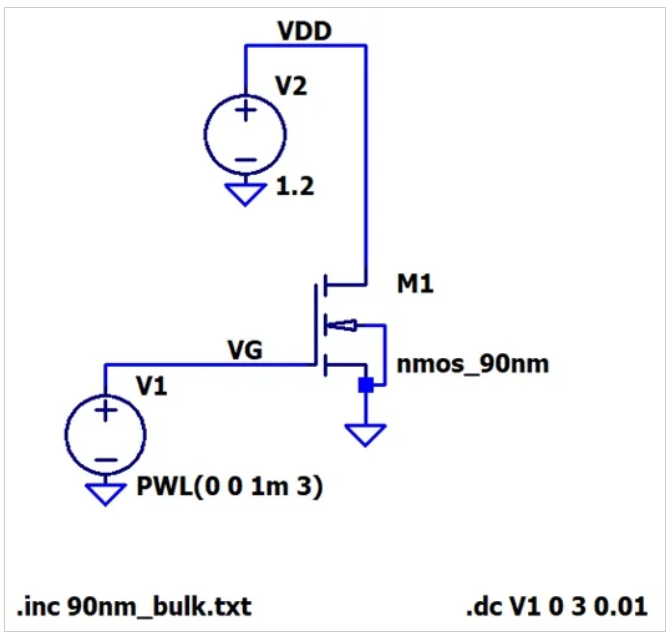

為了使LTspice可以訪問這些模型,您所需要做的就是插入一個SPICE指令,其中包含.inc[filename]。圖4中的示意圖中的庫名稱用綠色圈出,這樣您就可以看到它的樣子。

PTM 90 nm CMOS模型的基本FET電路。

圖4。具有PTM 90nm CMOS模型的基本NMOS晶體管的LTspice示意圖。圖片由Robert Keim提供

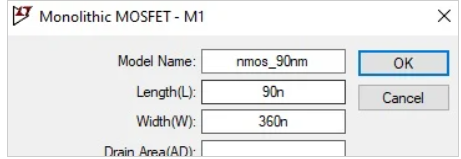

插入nmos4組件后,右鍵單擊它并選擇長度和寬度值(圖5)。確保“模型名稱”字段與SPICE模型文本文件中使用的名稱匹配。

選擇LTspice中NMOS晶體管的長度和寬度。

圖5。選擇LTspice中NMOS晶體管的長度和寬度。圖片由Robert Keim提供

對于這個MOSFET,我選擇了90納米的長度和360納米的寬度。

繪制漏極電流和柵極電壓

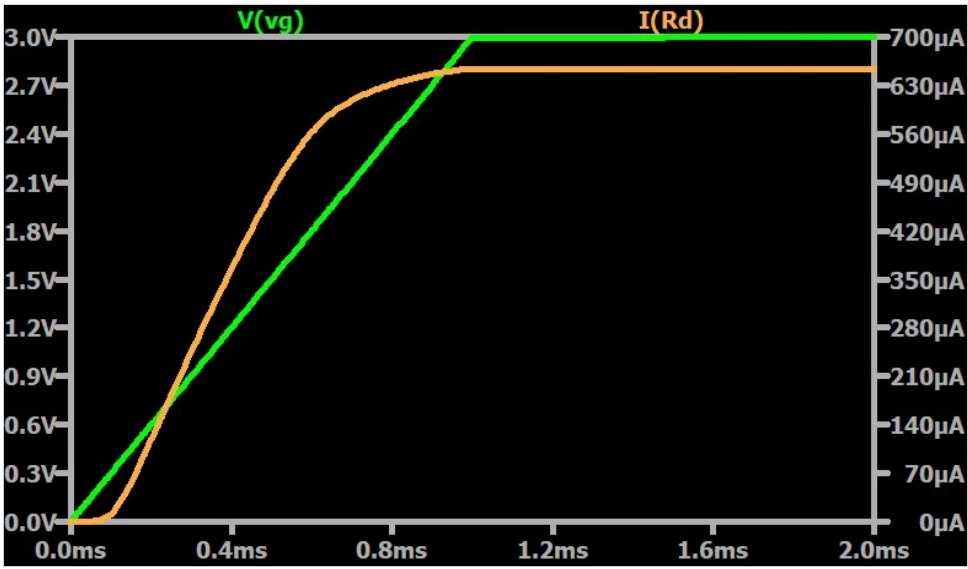

我們可以使用圖4的示意圖對該電路進行快速檢查,并確定其近似閾值電壓。請注意:

柵極-源極電壓從0V線性增加到3V,然后變為電平。

VDD是常數1.2V。

圖6顯示了2ms瞬態模擬的結果。

模擬NMOS晶體管的漏極電流和柵極電壓與時間的關系圖。

圖6。模擬的90nm NMOS晶體管的漏極電流和柵極到源極電壓與時間的關系圖。圖片由Robert Keim提供

正如預期的那樣,當有足夠的柵極電壓(VGS)時,漏極電流開始流動,并且隨著VGS的增加而增加。如果我們放大上面的圖,我們可以看到漏極電流曲線開始更快地增加(圖7)。

當柵極到源極電壓大于大約300mV時,顯著的漏極電流可以流動。

圖7。當VGS大于約300 mV時,可能會流過大量漏極電流。圖片由Robert Keim提供

當柵極電壓達到其閾值時,漏極電流的流量會增加。因此,我們可以說該MOSFET的閾值電壓約為300mV。

測量閾值電壓

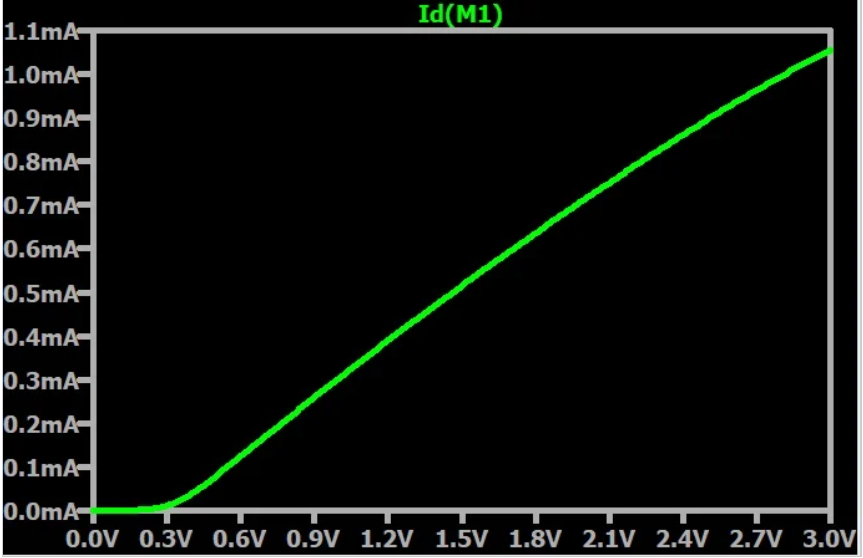

識別閾值電壓的一種更嚴格的方法是繪制漏極電流與VGS的關系圖,在這樣做的同時保持漏極到源極的電壓恒定。然后將所得曲線的線性部分延伸到x軸。該線性延伸與x軸相交的點是閾值電壓。

要執行此模擬,我們將使用圖8中的示意圖。

繪制漏極電流與柵極電壓關系的LTspice示意圖。

圖8。繪制漏極電流與柵極電壓關系的LTspice示意圖。圖片由Robert Keim提供

對之前的示意圖進行了兩次更改。首先,我們去掉了漏極電阻器——M1的漏極現在直接連接到VDD。這確保了我們具有1.2V的恒定漏極-源極電壓。

其次,.tran仿真命令已被.dc仿真命令所取代。新命令告訴LTspice以0.01V的步長從0V到3V線性地改變柵極電壓V1。它還使LTspice繪制模擬結果與V1值的關系圖,而不是與時間的關系圖。圖9顯示了最終的漏極電流圖。

漏極電流與柵極到源極電壓,漏極電壓保持恒定。

圖9。漏極電流與柵極-源極電壓的關系。漏極電壓保持恒定。圖片由Robert Keim提供

正如預期的那樣,漏極電流隨著柵極電壓的增加而穩步增加。接下來,我們放大并將曲線的線性部分延伸到水平軸(圖10)。

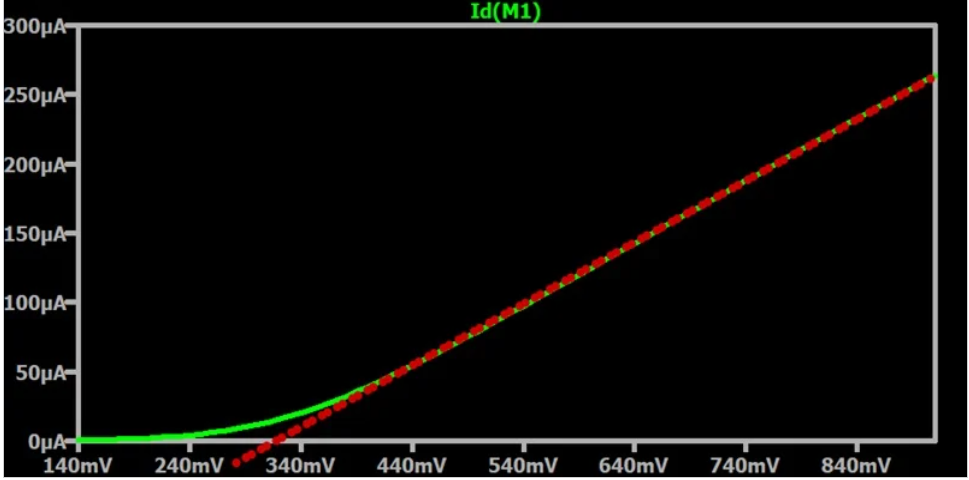

紅色虛線將漏極電流曲線的線性部分延伸到x軸。

圖10。紅色虛線將漏極電流曲線的線性部分延伸到x軸。圖片由Robert Keim提供

該方法為我們提供了大約320 mV的閾值電壓,這既接近于之前的近似值,也與我們對90 nm NMOS技術的期望一致。

下一篇

在本文中,我們使用LTspice和預測技術模型集合中的90nm CMOS模型來模擬基本NMOS電路并識別其閾值電壓。我們將在下一篇文章中討論其他表征技術。

評論