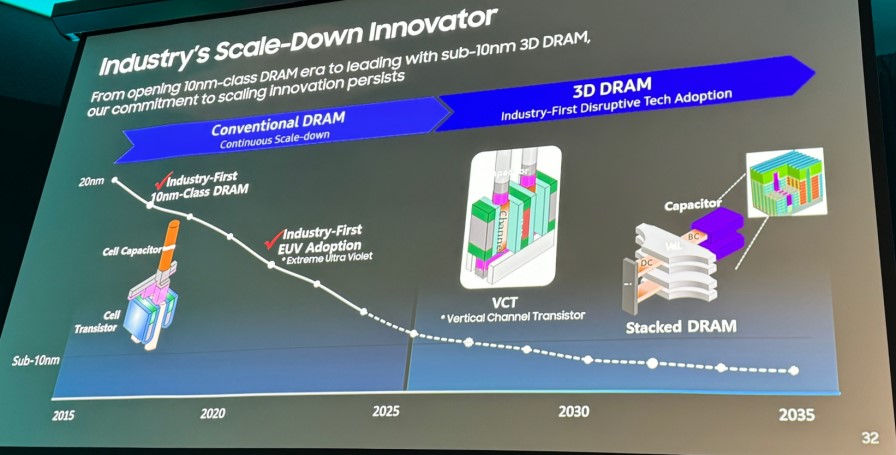

邁向 3D 內(nèi)存:三星電子計(jì)劃 2025 年完成 4F2 VCT DRAM 原型開發(fā)

IT之家 5 月 21 日消息,綜合韓媒 ZDNet Korea 和 The Elec 報(bào)道,三星電子執(zhí)行副總裁 Lee Siwoo 在本月舉行的 IEEE IMW 2024 研討會(huì)上表示該企業(yè)計(jì)劃在明年推出 4F2 VCT DRAM 原型。

本文引用地址:http://www.104case.com/article/202405/459001.htm目前 3D DRAM 領(lǐng)域商業(yè)化研究集中在兩種結(jié)構(gòu)上:

一種是 4F2 VCT(IT之家注:Vertical Channel Transistor,垂直通道晶體管) DRAM;另一種是 VS-CAT(Vertical Stacked-Cell Array Transistor,垂直堆疊單元陣列晶體管) DRAM。

前者主要是在 DRAM 單元結(jié)構(gòu)上向 z 方向發(fā)展,后者則是類似 3D NAND 一樣堆疊多層 DRAM。

▲ 圖源 Semiconductor Engineering

市面現(xiàn)有的 DRAM 內(nèi)存采用 6F2 結(jié)構(gòu),換用 4F2 結(jié)構(gòu)可縮減約 30% 面積,提高存儲(chǔ)密度,不過(guò)也對(duì) DRAM 材料提出了更高的要求。

除通過(guò)堆疊提升容量外,VS-CAT DRAM 還能降低電流干擾。三星電子預(yù)計(jì)其將采用存儲(chǔ)單元和外圍邏輯單元分離的雙晶圓結(jié)構(gòu),因?yàn)檠永m(xù)傳統(tǒng)的單晶圓設(shè)計(jì)會(huì)帶來(lái)嚴(yán)重的面積開銷。

在分別完成存儲(chǔ)單元晶圓和邏輯單元晶圓的生產(chǎn)后,需要進(jìn)行晶圓對(duì)晶圓(W2W)混合鍵合,才能得到 VS-CAT DRAM 成品,這一過(guò)程類似于長(zhǎng)江存儲(chǔ)在 3D 閃存中使用的 Xtacking 技術(shù)。

目前三星電子已在內(nèi)部實(shí)現(xiàn)了 16 層堆疊的 VS-CAT DRAM,美光方面處于 8 層堆疊的水平。

三星電子還在會(huì)議上探討了將 BSPDN 背面供電技術(shù)用于 3D DRAM 內(nèi)存的可能性,Lee Siwoo 認(rèn)為該技術(shù)有助于于未來(lái)對(duì)單個(gè)內(nèi)存 bank 的精細(xì)供電調(diào)節(jié)。

評(píng)論