Rambus推出面向高性能數據中心和人工智能SoC的PCIe 6.0接口子系統

作為業界領先的芯片和半導體IP供應商,致力于使數據傳輸更快更安全,Rambus Inc.(納斯達克股票代碼:RMBS)今日宣布,推出由PHY和控制器IP組成的PCI Express?(PCIe?)6.0接口子系統。Rambus PCIe Express 6.0 PHY還支持最新版本(3.0版本)的Compute Express Link?(CXL?)規范。

本文引用地址:http://www.104case.com/article/202212/441140.htm

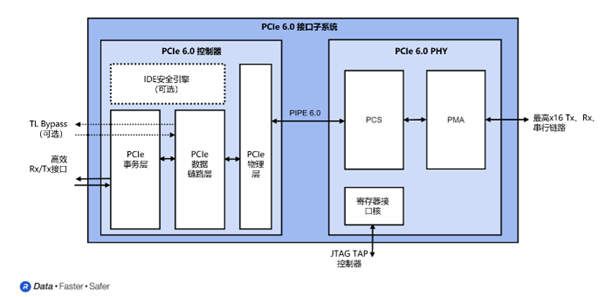

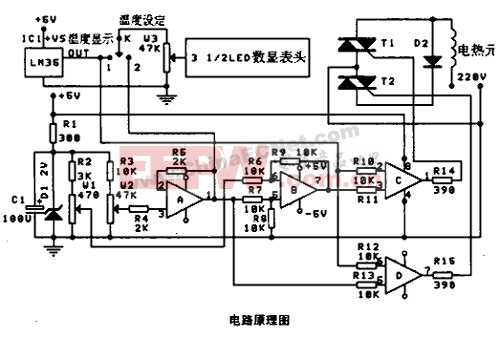

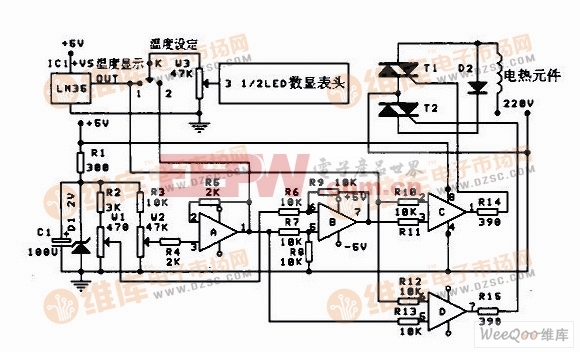

PCIe 6.0接口子系統(圖片來源:Rambus Inc.)

Rambus接口IP總經理Scott Houghton表示:“人工智能/機器學習(AI/ML)和數據密集型工作負載的快速發展正在推動數據中心架構的持續演進,并要求更高的性能水平。Rambus PCIe 6.0接口子系統可通過一流的延遲、功耗、面積和安全性,支持下一代數據中心對性能的要求。”

Rambus PCIe 6.0接口子系統的數據傳輸速率高達64GT/s,并且經過全面優化,可滿足先進異構計算架構的需求。該子系統中的PCIe控制器具備完整性和數據加密(IDE)引擎,專門用于保護PCIe鏈接和通過它們傳輸的重要數據。另外在PHY方面,它還提供對CXL 3.0的全面PHY支持,支持緩存一致性內存共享、擴展和池化的芯片級解決方案。

IDC計算半導體研究副總裁Shane Rau表示:“PCIe在數據中心無處不在。為了支持新一代應用的更高性能要求,企業正在不斷提升速度和帶寬,進而使CXL的重要性日益提升。越來越多的芯片公司開始支持新的數據中心架構,因此獲得高性能接口IP解決方案將成為實現該生態系統的關鍵。”

Rambus PCIe 6.0接口子系統有以下主要特性:

· 支持PCIe 6.0規范,包括64 GT/s數據傳輸速率和PAM4調制信號

· 支持固定尺寸的FLIT,可實現高帶寬效率

· 向后兼容PCIe 5.0、4.0和3.0/3.1

· 通過IDE引擎(控制器)實現最先進的安全性

· 支持CXL 3.0,用于優化內存資源的新使用模式(PHY)

評論