用于電源SiP的半橋MOSFET集成方案研究

0 引言

隨著電子技術的快速發展和終端應用場景更加苛刻,小型化電源的需求越來越迫切。實現小型化的有效方法之一是采用系統級封裝(System in Package,SiP)設計。其理念是采用裸芯片,通過多芯片組裝,最終形成具有完整電源功能的封裝產品。相較基于分立封裝器件的電源產品,電源SiP 的基板面積降至10%~20%,在性能、成本等方面也具有優勢[1]。

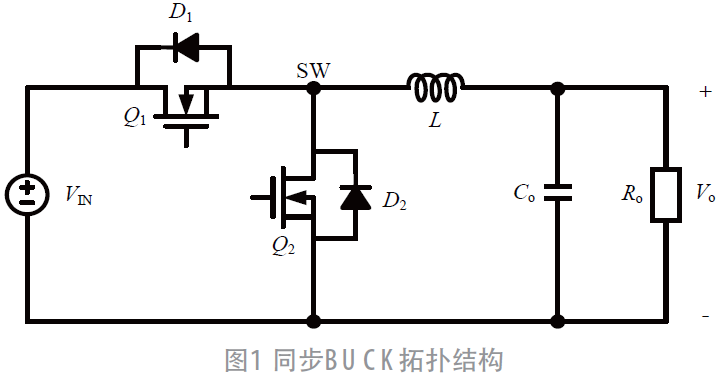

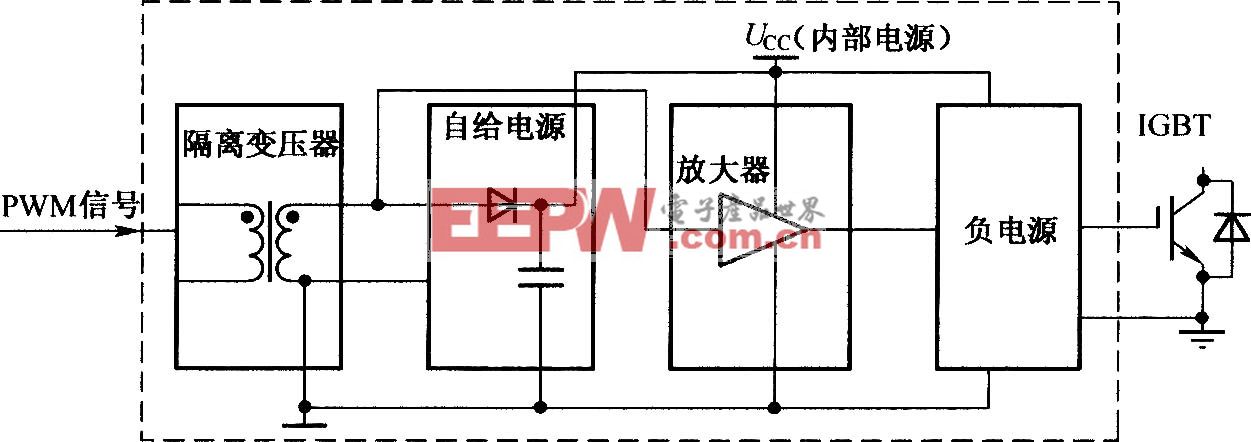

為提高大功率電源SiP 效率,一般將傳統開關電源拓撲中的續流二極管同步MOSFET 取代形成如圖1 所示的同步開關電源拓撲,2 個MOSFET Q1 和Q2 形成半橋結構。MOSFET 是影響電源效率、熱環境等性能的關鍵器件[2]。因此,半橋MOSFET 的集成方案需要全面論證,以滿足SiP 封裝尺寸、載流能力、熱阻、工藝、組裝維修等方面的需求。

本文討論了同步開關電源拓撲中的半橋MOSFET的基板表面平鋪、腔體設計、3D 堆疊等布局方法,以及鍵合絲、銅片夾扣等互連方式,通過對比不同方案的優缺點,為電源SiP 方案設計提供參考。

1 MOSFET裸芯片結構

功率開關MOSFET 有3 個端口,即漏極、源極和柵極。一般裸芯片的背面設計為漏極,正面是源極和柵極。源極和漏極的面積大,為大電流路徑。正反兩面根據實際應用濺射不同金屬層。如圖1 所示的半橋MOSFET 結構中,上管Q1 的源極與低邊的MOSFET Q2的漏極互連在一起。

2 半橋MOSFET布局方法

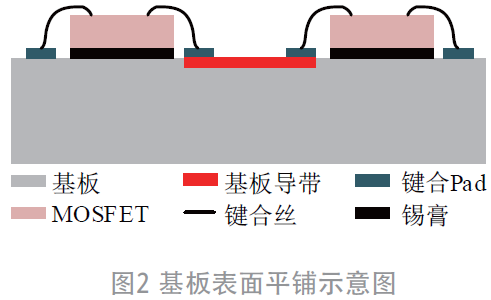

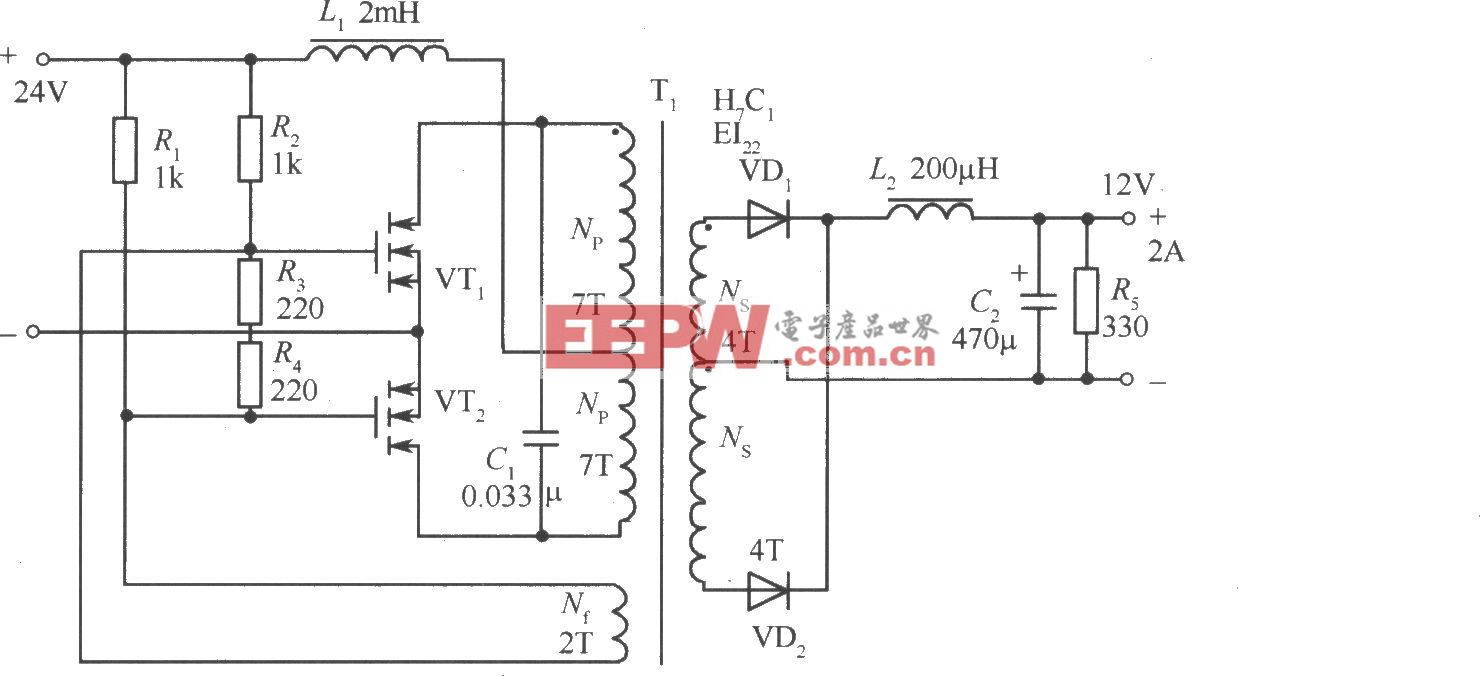

2.1 基板表面平鋪

半橋MOSFET 的平鋪布局如圖2 所示。為提高電源SiP 的散熱性能,降低大電流路徑的互連電阻,裸芯片背面的漏極通過錫膏燒焊到基板表面。正面的源極和柵極可通過鍵合絲或銅片夾扣連接到基板的焊盤上[3]。兩芯片的源漏通過基板的銅導帶實現互連。由于在基板表面,芯片的組裝維修都十分便利。

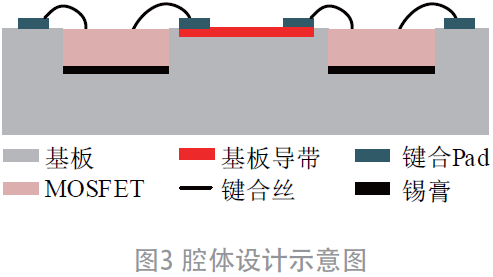

2.2 腔體設計

平鋪布局要求基板表面和芯片間有安全距離。為減小封裝面積,可以采取如圖3 所示的腔體設計,即將基板的外層開放式開窗,將MOSFET 芯片燒焊在內層,基板鍵合焊盤仍在表面[4]。受電源SiP 空間限制,腔體開窗面積對芯片的組裝修改產生一定的影響。腔體設計節省了基板焊盤和芯片間的距離,有利于電源SiP 整體尺寸的減小。

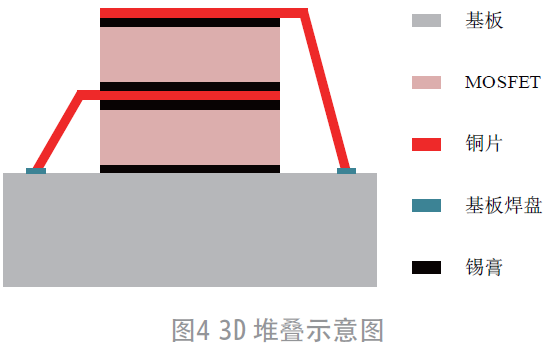

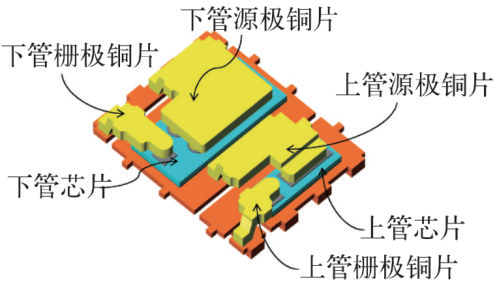

2.3 3D堆疊

如圖4 所示,半橋MOSFET 可采用縱向3D 堆疊減小封裝面積。兩芯片的源極、漏極及與基板導帶的互連一般采用銅片夾扣[5]。芯片與銅片間仍通過錫膏燒焊互連。3D 堆疊對組裝要求高,芯片焊接偏移需控制嚴格,避免與柵極鍵合絲短路;并且芯片維修的便利性差。

3 互連工藝

3.1 引線鍵合工藝

引線鍵合以技術成熟、工藝簡單、成本低廉、適用性強等特點而在電子工程互連中占據重要地位[5]。由于鋁絲/ 硅鋁絲的導電能力強,價格低廉、延展性好,所以常用作MOSFET 的鍵合引線。

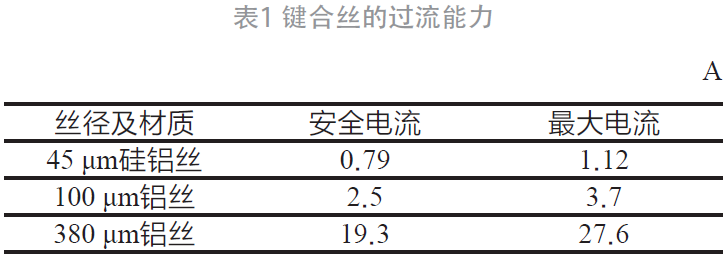

鍵合絲的材料和絲徑影響MOSFET 的過流能力,表1 是常見的鍵合絲徑及其過流能力。

3.2 銅片夾扣工藝

銅片夾扣鍵合是通過回流焊接的方式,將有特殊形狀的銅片焊接于芯片上,實現2 個MOSFET 的源漏極和基板導帶的互連。銅片的形狀與芯片開窗尺寸和版圖設計相關,避免與芯片柵極走線和鍵合絲短路。MOSFET 芯片表面需要濺射焊錫可浸潤的金屬材料,如鈦鎳金等,工藝比較復雜。

*25 A 為32 根45 μm 絲徑的硅鋁絲并聯鍵合,20 A為8 根100 μm 絲徑的鋁絲并聯鍵合

4 半橋MOSFET集成方案

在本節討論中,功率SiP 設計要求輸出電流達30 A;尺寸小于15 mm×15 mm,以滿足整機對電源小型化的需求。因此,選用的某型號MOSFET 裸芯片,其常溫下最大持續漏極電流為95 A,尺寸為4 mm×4 mm。通過討論不同布局和互連方式的優缺點,確定滿足電源SiP 要求的方案。

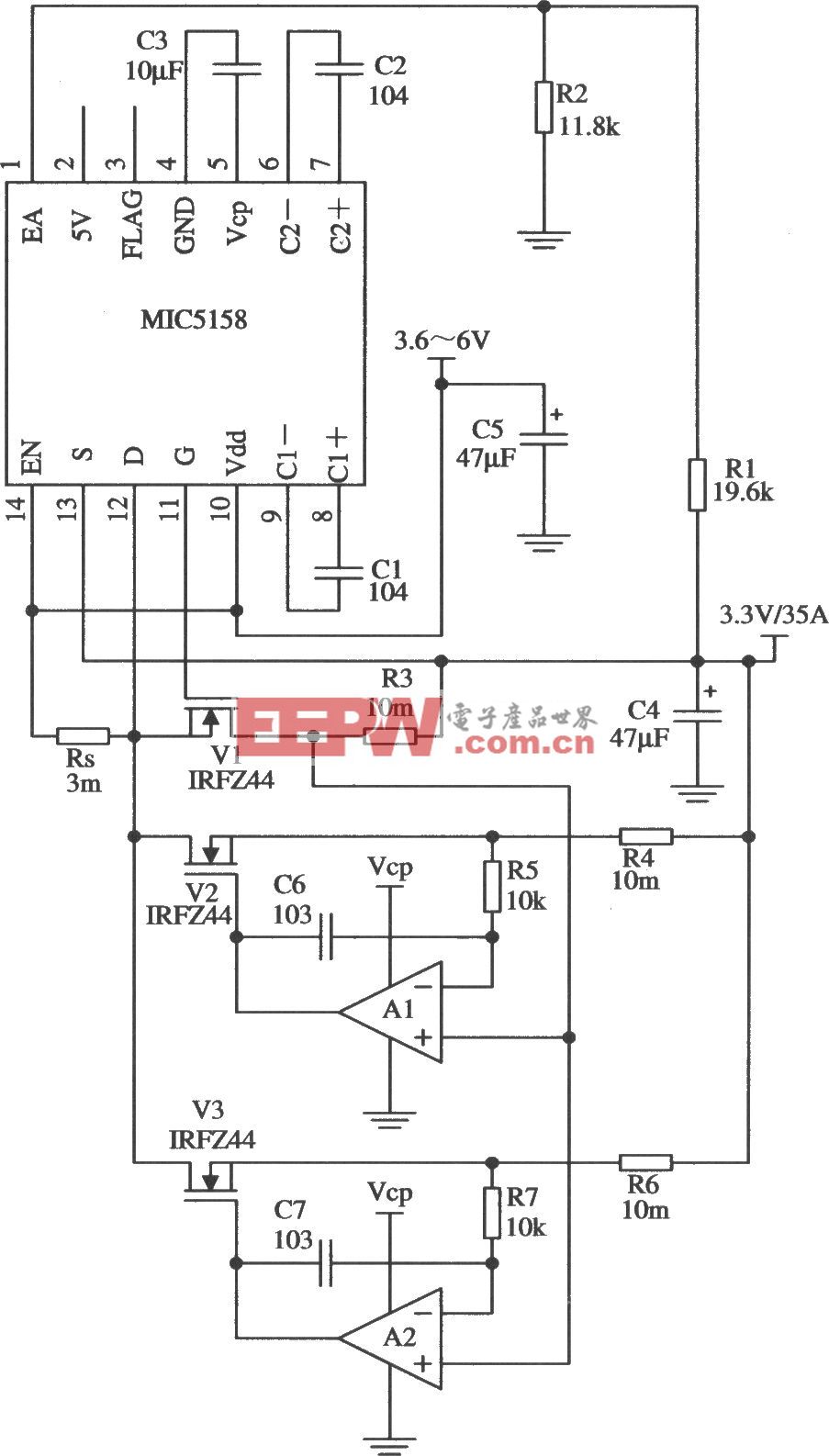

4.1 基板表面平鋪鍵合方案

基板鍵合焊盤尺寸設計為4 mm×0.5 mm,滿足源極多鍵合絲并聯要求。鍵合焊盤和芯片燒焊焊盤的安全距離定為0.25 mm。則2 個MOSFET 的總封裝面積約為38 mm2。鍵合絲有兩種選擇。選擇1 是MOSFET 的源極和柵極采用相同的45 μm 絲徑的硅鋁絲。源極最多能鍵合32 根硅鋁絲并聯,由表1 知MOSFET 的安全電流達25 A。選擇2 是MOSFET 的柵極和源極分別采用45 μm 絲徑的硅鋁絲和100 μm 絲徑的鋁絲。源極最多能鍵合8 根鋁絲并聯,安全電流達到20 A。在基板表面平鋪方案中,MOSFET 熱量主要是通過漏極單面向基板傳導。

4.2 基板表面平鋪銅片夾扣方案

基板表面平鋪銅片夾扣方案如圖5 所示。MOSFET源極互連改為0.2 mm 厚度的銅扣,可承受164 A 電流。受MOSFET 的持續漏極電流限制,該方案的半橋MOSFET 的載流能力為95 A。銅扣在基板上的焊盤尺寸設計為4 mm×1.5 mm,則封裝面積約為46 mm2。大面積銅片幫助MOSFET 的熱量雙面向基板傳導,極大地降低了芯片的熱阻。

圖5 基板表面平鋪銅片夾扣方案示意圖[5]

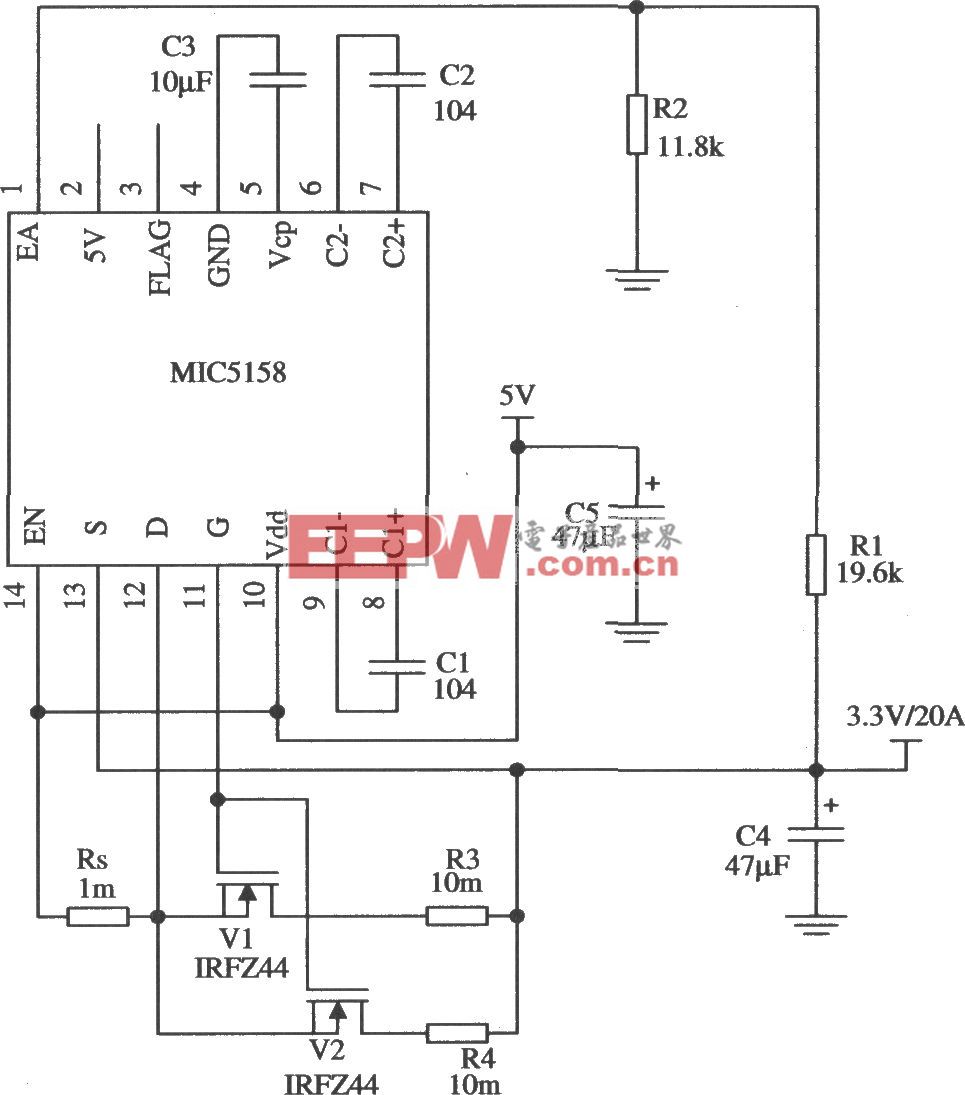

4.3 腔體設計鍵合方案

在腔體設計中,為了組裝和維修,開窗面積設計為4 mm×4.2 mm。該方案的鍵合設計同方案4.1,則需要37.6 mm2 的封裝面積,安全電流為25 A(32 根45 μm絲徑的硅鋁絲并聯)或20 A(8 根100 μm 絲徑的鋁絲并聯)。

4.4 腔體設計銅片夾扣方案

該方案的銅扣互連設計同方案4.2,開窗設計同方案4.3,需要45.6 mm2 的封裝面積,載流能力為95 A。和方案4.1 和4.2 對比,腔體設計對半橋MOSFET封裝面積改善不多。但是可減小MOSFET 芯片與周圍器件焊盤的距離,從而減小了電源SiP 整體封裝尺寸。由于MOSFET 燒焊在基板內層,相對于基板表面平鋪方案,散熱性略差,可通過適當增加散熱鋪銅面積改善熱阻。

4.5 3D堆疊銅片夾扣方案

3D 堆疊通過利用縱向空間提高封裝效率。若銅扣在基板上的焊盤尺寸同方案4.2,該方案可將半橋MOSFET 的封裝面積減小至30 mm2。兩片銅扣使芯片雙面散熱,極大地降低了熱阻。

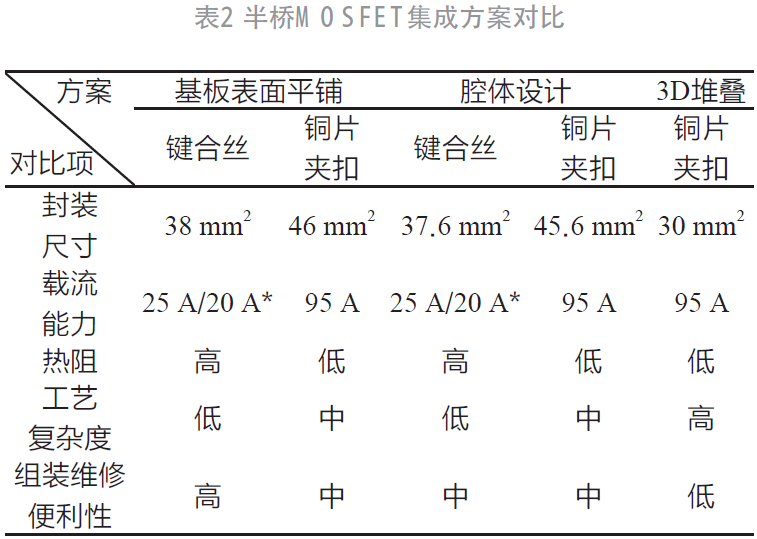

4.6 方案對比

表2 概述了半橋MOSFET 不同集成方案的優缺點。基板表面平鋪鍵合和腔體設計鍵合方案的工藝復雜度低,組裝維修便利性好,但是無法滿足電源SiP 輸出電流的要求。基板表面銅片夾扣方案在熱阻、工藝復雜度和組裝維修便利性之間取得了較好的平衡,但是封裝尺寸不利于電源SiP 的小型化設計。3D 堆疊銅片夾扣方案具有最小的封裝面積和很好的導熱性能,但是工藝復雜度高,組裝維修便利性低。腔體設計銅片夾扣是相對折中的方案,可以滿足電源SiP 設計要求。

5 結束語

本文討論了半橋MOSFET 不同集成方案。為滿足電源SiP 輸出電流達30 A,尺寸小于15mm×15 mm 的要求,相對折中的方案是采用腔體設計銅片夾扣方案。該方案的載流能力達到了MOSFET 的最大持續漏極電流95 A;熱阻低;因為節省了MOSFET 裸芯片與周圍焊盤的距離,有利于電源SiP 的小型化。

參考文獻:

[1] 李揚.SiP系統級封裝設計仿真技術[J].電子技術應用,2017,43(7):47-50,54.

[2] 陳帥,郗小鵬,張勇.同步BUCK變換器中MOSFET選型應用研究[J].單片機與嵌入式系統應用,2019(11):75-77,81.

[3] 王其超,季睿,姚佳.一種應用于GaN功放的高壓電源調制器設計[J].工業控制計算機,2021,34(6):134-135.

[4] 李揚.3D設計技術在SiP中的應用[J].電子技術應用,2018,44(9):39-43.

[5] 霍炎,吳建忠.銅片夾扣鍵合QFN功率器件封裝技術[J].電子與封裝,2018,18(7):1-6.

[6] 陳宏仕.MOSFET 器件引線鍵合技術[J]. 電子與封裝,2010,10(7):1-3.

(本文來源于《電子產品世界》雜志2021年12月期)

評論