EdgeBoard中“活靈活現”的算子

背景介紹

本文引用地址:http://www.104case.com/article/201912/408763.htm數據、算法和算力是人工智能技術的三大要素。其中,算力體現著人工智能(AI)技術具體實現的能力,實現載體主要有CPU、GPU、FPGA和ASIC四類器件。CPU基于馮諾依曼架構,雖然靈活,卻延遲很大,在推理和訓練過程中主要完成其擅長的控制和調度類任務。GPU以犧牲靈活性為代價來提高計算吞吐量,但其成本高、功耗大,尤其對于推理環節,并行度的優勢并不能完全發揮。專用ASIC芯片開發周期長,資金投入大,由于其結構固化無法適應目前快速演進的AI算法。FPGA因其高性能、低功耗、低延遲、靈活可重配的特性,被廣泛地用作AI加速,開發者無需更換芯片,即可實現優化最新的AI算法,為產品贏得寶貴的時間。

由此,百度基于FPGA打造了EdgeBoard嵌入式AI解決方案,能夠提供強大的算力,支持定制化模型,適配各種不同的場景,并大幅提高設備端的AI推理能力,具有高性能、高通用、易集成等特點。本文將主要介紹EdgeBoard中神經網絡算子在FPGA中的實現。

FPGA加速的關鍵因素

FPGA實現AI加速有兩大關鍵因素,一是FPGA內部資源,二是內存訪問帶寬。FPGA內部資源主要包括LUT,FF,RAM以及DSP等,FPGA本質上是可編程邏輯電路,可用邏輯電路的多少取決于芯片內部資源,這也就決定了芯片的峰值算力和可容納的算子種類數。

在深度學習中,90%以上的計算都集中在conv、dw-conv和pooling等少數的幾個算子上。所以,并不是FPGA中添加的加速算子數量越多越好,而是要注重算子的加速質量:一是用更少的資源實現更多的功能;二是提高耗時占比大的算子性能。

在實踐中,添加新算子前需要平衡該算子在網絡中所耗時間的占比以及其在FPGA中所消耗的資源。當然可以通過選取更大規模的片子來突破這種限制,但是端上設備受限于成本、功耗等因素,只能平衡多種因素選擇一個合適規模的芯片,然后通過多種設計方法和技巧來提高加速性能。本文接下來就將介紹在EdgeBoard中如何優化設計DSP資源提升算力,以及如何通過算子復用和融合技術實現對多算子的支持。

提升內存訪問帶寬是提高AI加速性能的另一關鍵因素,因為FPGA與內存的數據交互在整個計算過程中占比很高,有時甚至超過了計算本身所消耗的時間。直接提高內存訪問帶寬的方法包括提高DDR位寬、增加傳輸所用的高速接口資源、提高DMA傳輸的時鐘頻率等。另外也可以通過復用FPGA芯片上的內存資源(RAM)以及計算和傳輸交疊執行(overlap)等方法,減少與外部DDR存儲的交互,降低數據傳輸的開銷。這些設計方法較為常見,本文不做詳細介紹。

兩大關鍵技術實現四倍算力提升

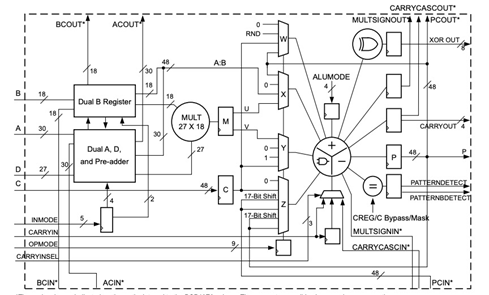

FPGA中的計算主要依靠DSP實現,高效使用DSP是保證FPGA算力的關鍵。EdgeBoard FPGA中的DSP采用DSP48E2架構,如圖1所示,包括一個27-bit的預加法器(pre-adder),一個27x18的乘法器(mult)和一個48-bit的ALU。

圖1. DSP48E2結構圖

在EdgeBoard的FPGA設計中,充分利用DSP48E2本身的特點,采用supertile和INT8移位計算技術,實現了四倍算力提升。

一.Supertile

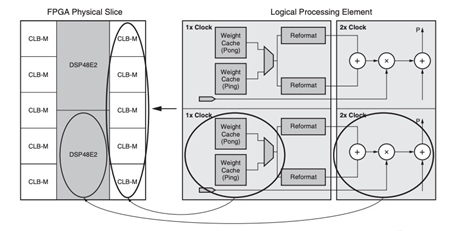

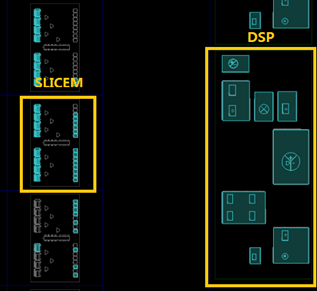

一般來講,Xilinx Ultrascale系列FPGA運行的最高頻率在300MHz到400MHz之間,但DSP是FPGA中的硬核,可以運行在更高的頻率上。如圖2所示,SLB-M與DSP這樣構成的基本單元,被稱之為Supertile,FPGA內部Supertile的布局如圖3所示。Supertile技術的核心在于使DSP運行于兩倍邏輯頻率上,使整個系統算力達到倍增的效果。這主要得益于芯片結構中SLICEM與DSP位置臨近,使用專有的布線資源,延遲縮短,可以支撐SLICEM以雙倍邏輯運行的頻率向DSP提供數據。另外,神經網絡中存在著數據復用,通過filter和image數據的復用和交織,一次取數多次使用,從而減少數據的搬運次數,提升計算效率。

圖2. Supertile結構

圖3. DSP和SLICEM在FPGA中的位置

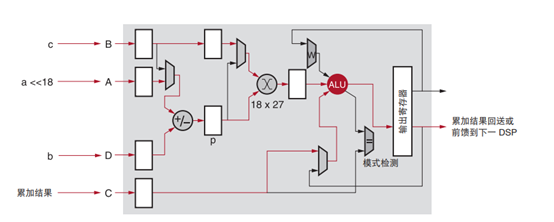

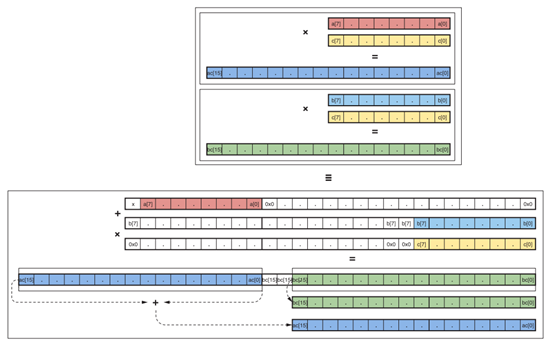

二.INT8移位計算技術

利用DSP48E2的結構特點,一個DSP完成兩路INT8的乘加。在進行8bit數據計算時,將a左移18位,置于輸入的高8位,低19位補0,從DSP的A端輸入,b維持在低8位,從DSP的D端輸入,如圖4所示。a與b兩者先進行累加,然后與c相乘后,結果將分別位于輸出的高(a*c)、低(b*c)兩部分,該計算過程如圖5所示。

圖4. DSP移位示意圖

圖5.單DSP實現兩路INT8相乘

在實踐中,我們把a,b兩路作為filter數據輸入,c作為image數據輸入。這樣DSP在一個時鐘周期內就同時完成了兩路的計算,再次使算力翻倍。結合前面提到的supertile倍頻設計,兩種設計使得單個DSP的算力提升四倍。因為一次計算過程有乘、加兩個操作(operations),所以單個DSP在一個時鐘周期高效的完成了8個operations。

多算子復用

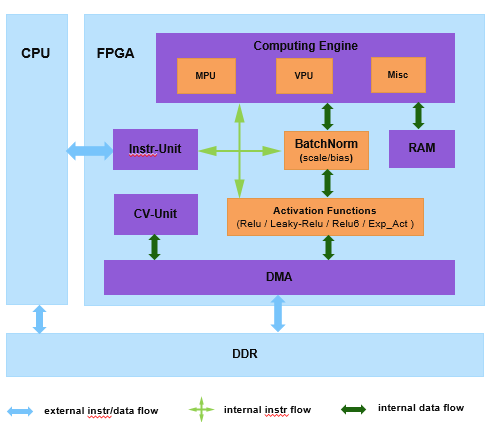

深度學習中主要有兩類運算,一類是指數運算,另一類是乘加運算。前者主要位于激活函數層,后者是深度學習涉及最多也是最基礎的運算。乘加運算根據kernel的維度不同,又可分為向量型和矩陣型,在EdgeBoard中劃分為三個運算單元,分別為向量運算單元(VPU: vector processing unit)、矩陣運算單元(MPU: matrix processing unit)和指數激活運算單元(EXP-ACT: exponential activation unit)。

一.向量運算單元

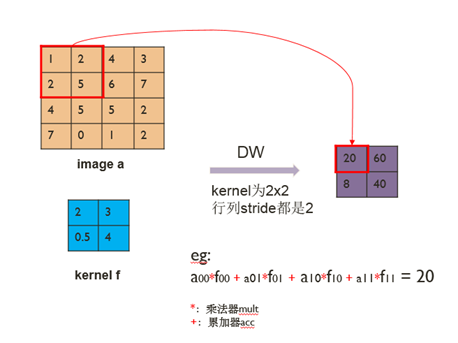

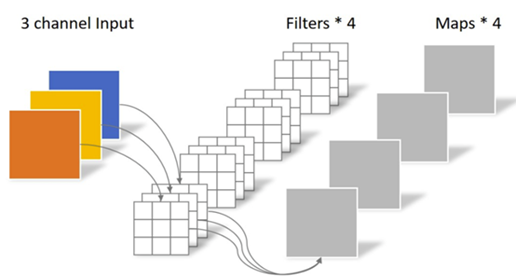

向量運算單元VPU負責實現dw-conv(depth-wise convolution),完成3維輸入圖像(H x W x C)和3維卷積核(K1 x K2 x C)的乘加操作。其中一個卷積核負責輸入圖像的一個通道,卷積核的數量與上一層的通道數相同,該過程如圖6所示。圖7表示的是一個通道內以kernel 2x2和stride 2為例的計算過程。

圖6. dw-conv示意圖

圖7. dw-conv的計算

EdgeBoard通過復用VPU一套計算資源實現了average/max pooling,elementwise add/sub,scale,batch-normalize,elementwise-mul和dropout等多種算子。

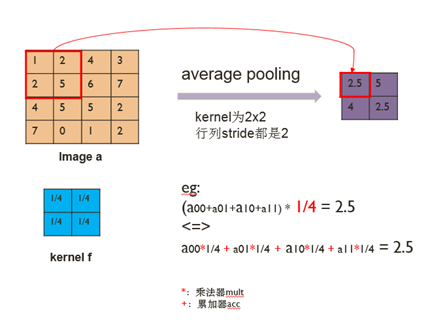

1.Average pooling可以看作是卷積核參數固定的dw-conv,即將求和后取平均(除以卷積核面積)的操作轉換成先乘以一個系數(1/卷積核面積)再求和。如圖8所示,該例子中卷積核大小為2x2,卷積核參數即為1/4。卷積核固定的參數可以類似于dw-conv下發卷積核的方式由SDK封裝后下發,也可以通過SDK配置一個參數完成,然后在FPGA中計算轉換,這樣節省卷積核參數傳輸的時間。另外,max-pooling算子與average pooling的計算過程類似,只需要將求均值操作換成求最大值的操作,其余挖窗、存取數等過程保持不變。

圖8. Pooling復用dw-conv

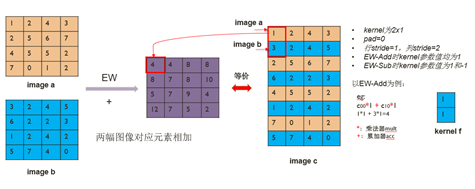

2.Elementwise add/sub完成兩幅圖像對應元素的相加或相減,不同于dw-conv的是它有兩幅輸入圖像。如果我們控制兩幅圖像的輸入順序,將兩幅圖像按行交錯拼成一幅圖像,然后取卷積核為2x1,行stride為1,列stride為2,pad均設置成0,則按照dw-conv的計算方式就完成了elementwise的計算。通過在FPGA中設置當前像素對應的kernel值為1或-1,就可以分別實現對應elementwise add和elementwise sub兩個算子。該過程如圖9所示。

圖9. ew-add/sub復用dw-conv

3.Scale算子主要在圖像預處理時使用,將輸入圖像每一個通道的全部像素點乘以該通道對應的scale值,然后加上bias。如果我們將dw-conv的卷積核大小設成1x1,行列stride都設置成1,pad設置成0,卷積核參數值設成scale,就可以通過dw-conv完成scale算子的功能。通過分析發現,batch-normalize,elementwise-mul和dropout等算子都可以通過scale算子來實現。

二.矩陣運算單元

矩陣運算單元MPU負責實現convolution,完成3維輸入圖像(H x W x C)和4維卷積核(N x K1 x K2 x C)的乘加操作,單個卷積核的通道數和輸入圖像的通道數相同,而卷積核的數量N決定了輸出的通道數,如圖10所示。full connection算子實現的1維輸入數組(長度C)和2維權重(N x C)的乘加操作。將 full connection輸入數組擴展成 H x W x C,輸出擴展成 N x K1 x K2 x C,其中H, W, K1和K2均設置成1,這樣 full connection就可以調用convolution來實現。另外,在計算 deconv時,通過SDK對卷積核進行分拆、重排,就可以通過調用conv來實現deconv,同樣帶來了極大的收益。

圖10. Conv算子示意圖

三.指數激活運算單元

指數激活運算單元EXP-ACT實現的基礎是sigmoid,由于在FPGA中進行指數型運算比較耗資源,如何復用該計算單元就變得非常有意義。通過分析發現,可以把 tanh和兩通道softmax轉換成 sigmoid的形式,這樣一個指數運算單元就支持了3種算子,實現資源利用的最大化。

多算子融合

在推理時做BatchNorm運算非常耗時,通過SDK將BatchNorm+Scale的線性變換參數融合到卷積層,替換原來的weights和bias,這樣4個算子可以融合成單個算子conv + batchnorm + scale + relu,對于dw-conv同樣如此。相對于每計算完一個算子就將數據送回內存,這種算子融合大大減少了內存的讀寫操作,有效提高了處理幀率。

此外,我們將scale、bias和relu為代表的激活函數層放到各算子之后的鏈路上,然后統一送到DMA傳輸模塊,如圖11所示。這不僅使得各算子復用了這些邏輯,節省了大量片內資源,也使得各算子都可以具備這些功能,且都能以最大帶寬進行DMA傳輸。在實踐中,我們將這些功能做成可選項,由軟件根據當前網絡算子的需要進行選擇,在節省資源的同時,既保證了通用性,又兼顧了靈活性。

圖11. EdgeBoard內部結構和鏈路圖

評論