Xilinx祭出Vitis統一軟件平臺,面向軟硬件和AI等所有開發者

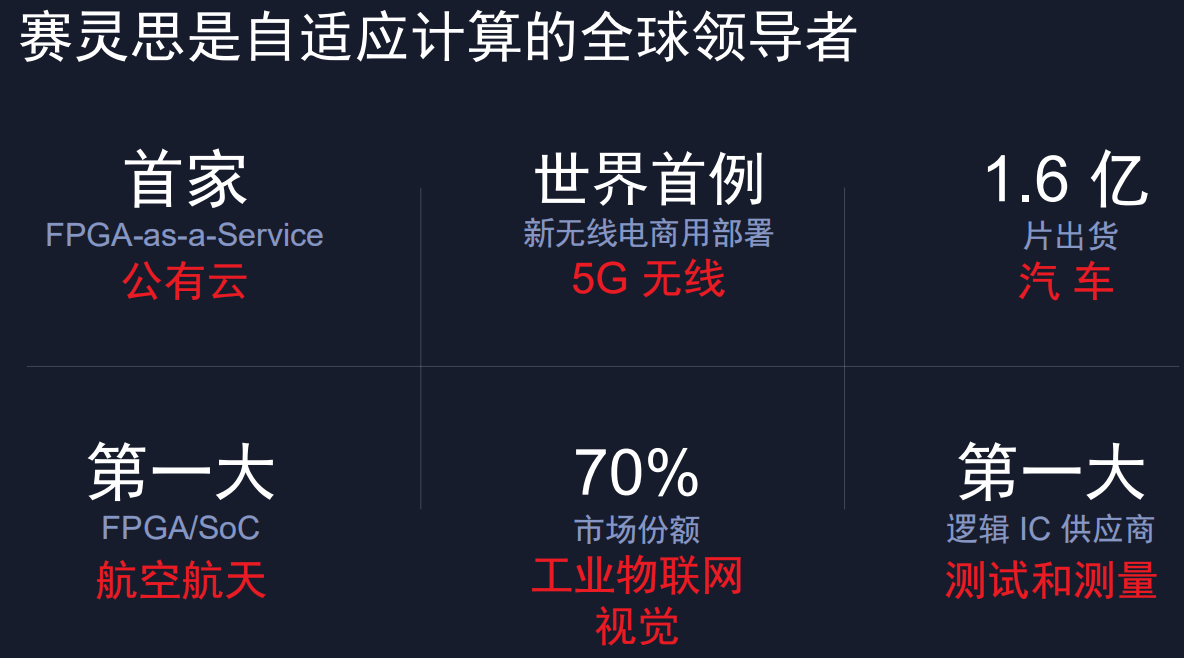

這幾年,很多芯片硬件公司在向軟件和生態環境方向下功夫。例如近日,賽靈思公司(Xilinx)發布重磅產品——Vitis統一軟件平臺,把應用領域拓得更寬,可以讓包括軟件工程師和 AI 科學家在內的廣大開發者受益于硬件靈活應變的優勢。

本文引用地址:http://www.104case.com/article/201910/405996.htm

Vitis 統一軟件平臺

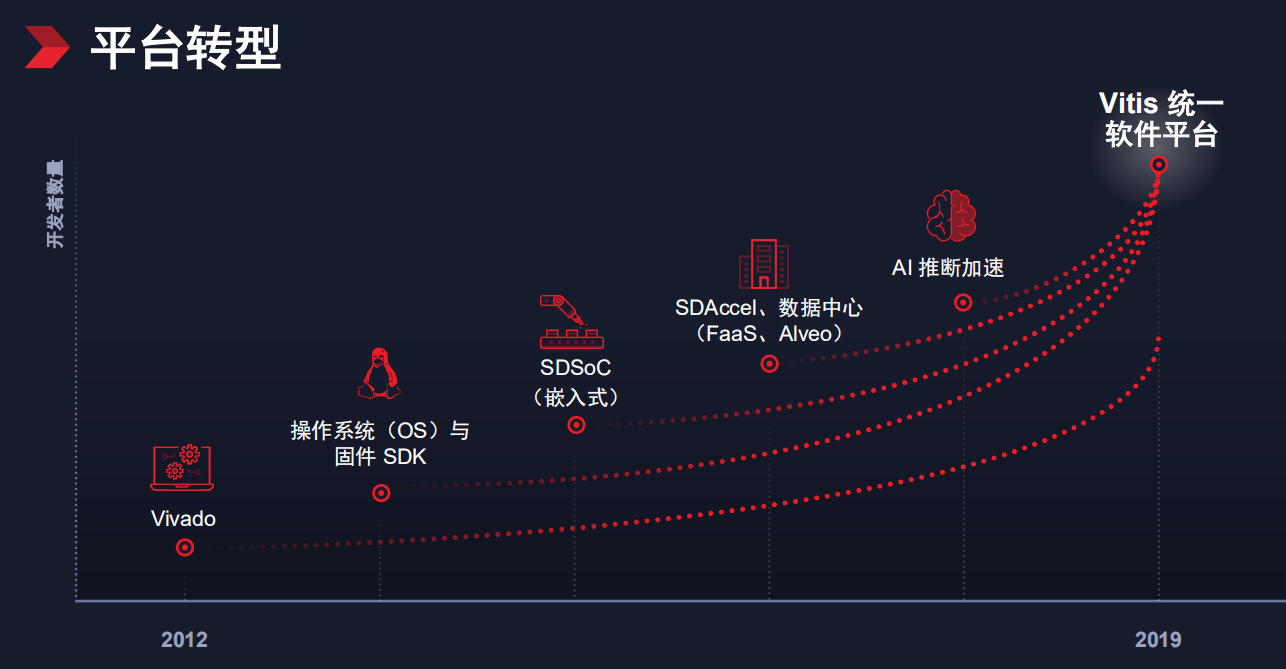

眾所周知,賽靈思是 FPGA、硬件可編程 SoC 及 ACAP(自適應加速平臺) 的發明者,這幾年一直向軟件方向和AI方向發力,以利于其硬件的開發和應用。前幾年就推出了Vivado設計套件,此次新的Vitis更進一步。

歷經五年、投入總計 1000 個人工年而打造,Vitis 統一軟件平臺無需用戶深入掌握硬件專業知識,即可根據軟件或算法代碼自動適配和使用賽靈思硬件架構。此外,Vitis 平臺不限制使用專有開發環境,而是可以插入到通用的軟件開發工具中,并利用豐富的優化過的開源庫,使開發者能夠專注于算法的開發。

那么,Vitis和原有的Vivado的關系如何?Vitis 獨立于 Vivado 設計套件,后者仍然繼續為希望使用硬件代碼進行編程的用戶提供支持。但是,Vitis 也能夠通過將硬件模塊封裝成軟件可調用的函數,從而提高硬件開發者的工作效率。

賽靈思大中華區銷售副總裁唐曉蕾在介紹 Vitis 發布的行業意義時指出,當前呈現邊緣與云端的統一化趨勢,以及人工智能飛速發展。隨著計算需求呈指數級增長,工程師與科學家常常受到固定芯片性能的局限。賽靈思打造的Vitis設計環境,使各學科領域的編程人員與工程師能夠使用他們已熟知并掌握的工具和框架,共同開發與優化他們的軟硬件。這意味著他們可以根據自己的應用調整硬件架構,而不需要新型芯片。

賽靈思軟件和人工智能高級經理羅霖介紹了里程碑式的Vitis統一軟件平臺,揭開了其如何通過軟件革新,解鎖軟件開發者的硬件加速壁壘,將其獨特的自適應計算能力帶給全員開發者的新篇章。

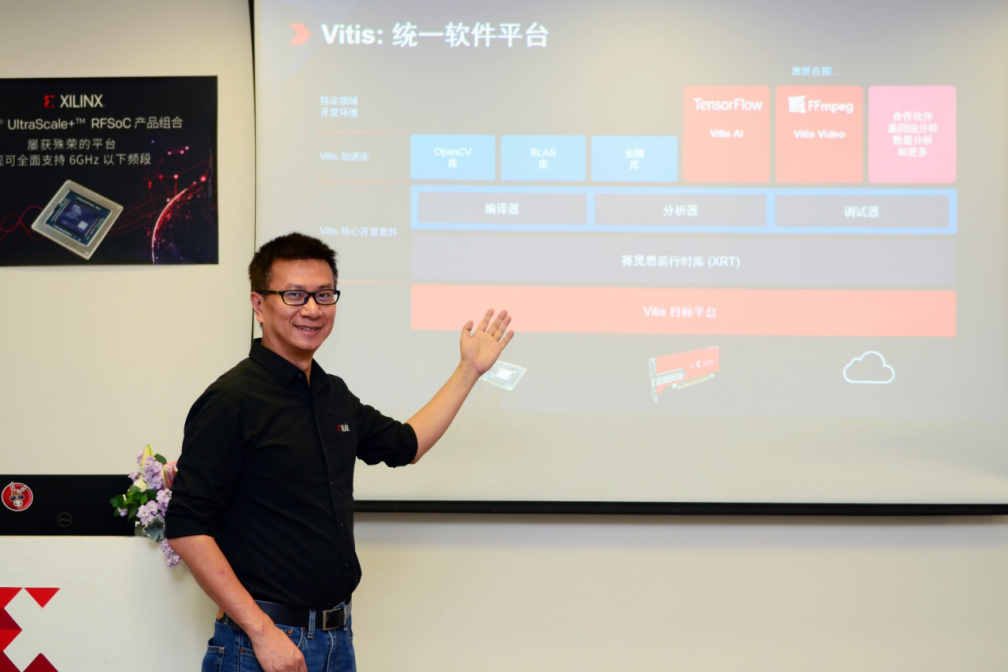

VITIS 堆棧

Vitis 平臺構建在基于堆棧的架構之上,該架構可以無縫插入到開源的標準開發系統與構建環境,而且最重要的是,它包含一套豐富的標準庫。

圖Vitis 堆棧

如上圖,基礎層是 Vitis 目標平臺。該平臺由電路板和預編程 I/O構成。

第2層稱為 Vitis 核心開發套件,覆蓋開源賽靈思運行時庫,以管理不同域間的數據移動,包括子系統、即將發布的 Versal ACAP內的 AI 引擎和必要的外部主機。此外,該層也提供編譯器、分析器和調試器等核心開發工具。雖然賽靈思提供的是一流的設計環境,但是這些工具設計的目的是能與業界標準的構建系統與開發環境無縫集成。

在第3層,8個Vitis 庫提供 400 余種優化的開源應用。這8個庫分別是:Vitis 基本線性代數子程序(BLAS)庫、Vitis 求解器庫、Vitis 安全庫、Vitis 視覺庫、Vitis 數據壓縮庫、Vitis 計量金融庫、Vitis 數據庫集和 Vitis AI 庫。借助這些庫,軟件開發者可以使用標準的應用編程接口(API)來實現硬件加速。

Vitis AI 和特定領域架構

Vitis 平臺的第 4 層,也是最具有變革意義的一層是 Vitis AI。它集成了特定領域架構(DSA)。DSA 提供了針對AI模型的硬件實現,開發者可以使用包括 TensorFlow 和 Caffe 等業界領先框架對其進行配置與編程。Vitis AI 提供的工具鏈能在數分鐘內完成優化、量化和編譯操作,在賽靈思器件上高效地運行預先訓練好的AI模型。此外,它也為從邊緣到云端的部署提供了專用 API,實現業界一流的推斷性能與效率。

賽靈思很快還將推出另一個 DSA(Vitis Video),支持從 FFmpeg 直接進行編碼并提供同樣超級簡單且功能極強大的端到端視頻解決方案。由合作伙伴公司提供的 DSA 包括:與 GATK 集成用于基因分析的Illumina,與ElasticSearch 集成用于大數據分析的BlackLynx,以及當前我們客戶正在使用的專有DSA。

VITIS 開發者網站

賽靈思還宣布推出了一個開發者網站,方便開發者獲取示例、教程和文檔,同時作為連接Vitis開發者社區的空間。它將由賽靈思和Vitis專家及愛好者共同管理,并將提供Vitis有關的最新更新、提示和技巧的寶貴信息。

評論