AMD公布3D封裝技術(shù):處理器與內(nèi)存、緩存通過硅穿孔堆疊在一起

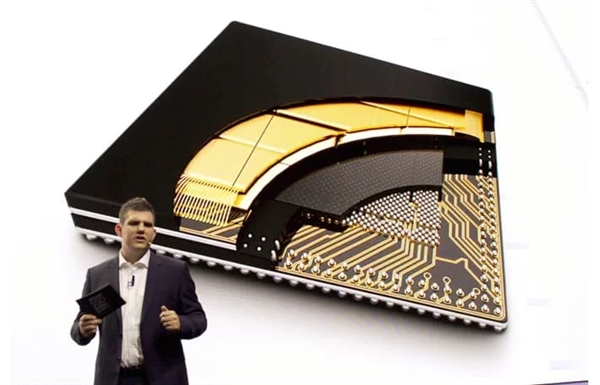

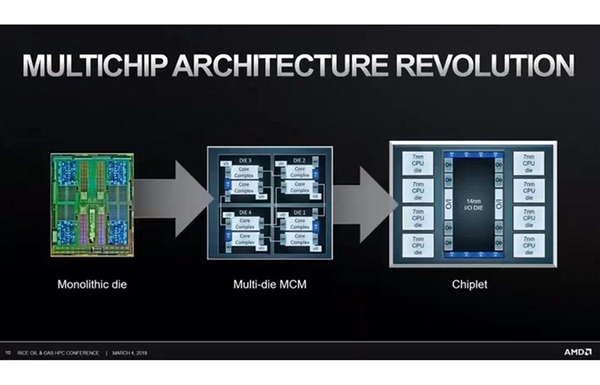

編者按:在Rice Oil&Gas高性能計(jì)算會(huì)議上,AMD高級(jí)副總裁Forrest Norrod介紹,他們正跟進(jìn)3D封裝技術(shù),目標(biāo)是將DRAM/SRAM(即緩存等)和處理器(CPU/GPU)通過TSV(硅穿孔)的方式整合在一顆芯片中。

目前的智能手機(jī)普遍實(shí)現(xiàn)了處理器SoC和內(nèi)存(DRAM)的堆疊式封裝(PoP),從AMD日前公布的信息來看,PC產(chǎn)品也有望實(shí)現(xiàn)類似的技術(shù)。

本文引用地址:http://www.104case.com/article/201903/398650.htm在Rice Oil&Gas高性能計(jì)算會(huì)議上,AMD高級(jí)副總裁Forrest Norrod介紹,他們正跟進(jìn)3D封裝技術(shù),目標(biāo)是將DRAM/SRAM(即緩存等)和處理器(CPU/GPU)通過TSV(硅穿孔)的方式整合在一顆芯片中。

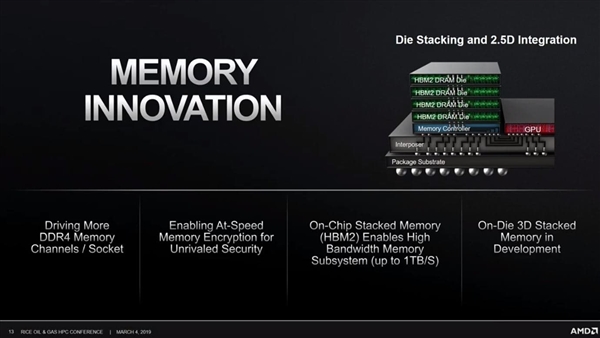

其實(shí)此前,AMD就率先推出了HBM顯存產(chǎn)品,實(shí)現(xiàn)了GPU芯片和顯存芯片整合封裝,但那僅僅屬于2.5D方案。

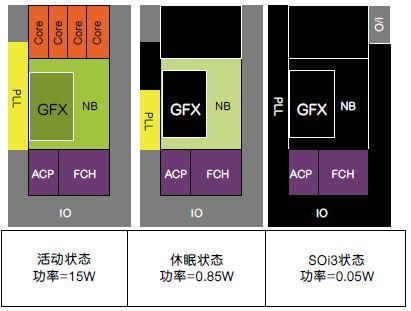

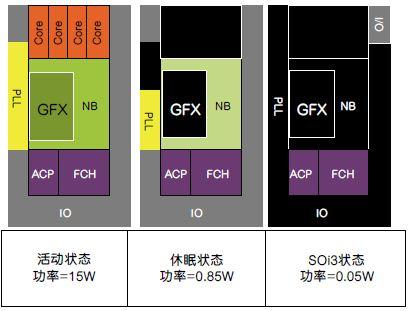

3D堆疊的好處在于縮短了電流傳遞路徑,也就是會(huì)降低功耗。不過,3D封裝的挑戰(zhàn)在于如何控制發(fā)熱。

遺憾的是,AMD并未公布更多技術(shù)細(xì)節(jié)。

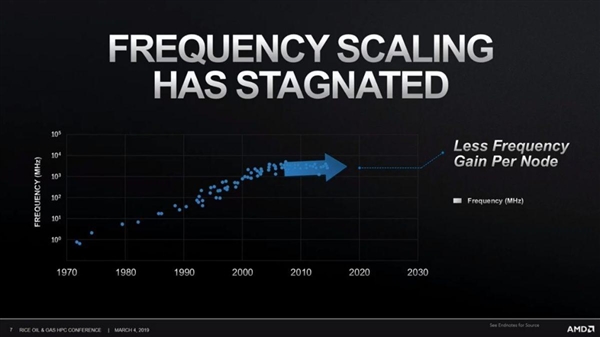

AMD稱,雖然光刻工藝在精進(jìn),但是頻率甚至要開始走下坡路,需要一些新的設(shè)計(jì)助力。

其實(shí)Intel今年也公布了名為Foveros的3D芯片封裝技術(shù),將22nm I/O基板、10nm Sunny Core和四核Atom整合在一起,功耗僅7瓦。

評(píng)論