基于軟件管理電源系統的硬件

假如您考慮到軟件團隊相對于其硬件伙伴所擁有的以下優勢,那么就可以體會出:電源系統設計師和數字 ASIC/FPGA/微處理器電路板設計人員對于從事軟件工程的同事略感 “羨慕” 或許是合乎情理的。

本文引用地址:http://www.104case.com/article/201809/388226.htm● 電路板硬件設計需要耗時幾天乃至數周,相比之下,從編寫軟件代碼到觀察其效果之間的時間延遲要短得多。對產品上市進程造成最大限制的是其編碼和測試生產率,而與其他因素關系不大。

● 軟件更新是根據需要 “推送” 給客戶,用以修補漏洞和改善現場使用性能。硬件更新則必需召回電路板進行返工。

● 他們可以在舒適的小隔間里通過記錄的數據輕松地跟蹤其代碼的性能。性能瓶頸一下子就可以確定,因而能在未來實現快速改進。而在另一塊場地上,硬件工程師們則是一連幾天呆在實驗室里,使用電壓計和示波器探頭彎腰駝背地的 “搗鼓” 各種電路板。

● 他們編寫一組核心模塊代碼,隨后針對不同的客戶和市場需求進行相應的修改。定制的硬件則需要變更組件和物料清單(BOM),因而冒著設計產生分歧的風險。

電源系統設計師面臨的挑戰日益嚴峻

使問題更加嚴重的是,隨著納米級處理器(ASIC、FPGA、微處理器、DSP) 的電源電壓持續降低至目前的不足1V,新式數字電路板的電源系統設計團隊面臨的挑戰就更加嚴峻。負載點(POL)電源的容限要求日益嚴格,已接近2%至3%,誤差預算包括負載步進時的DC準確度、紋波和瞬態偏移。請注意,0.9V 電源的3%僅為27mV。在電源電壓下降、處理器中塞進更多內核的同時,電流值卻在上升,甚至超過了100A。在數百安培電流流經電源及地平面的情況下保持數十毫伏的準確度是一個嚴峻的PDN(配電網絡)設計任務。與此同時,人們還在盡力提高處理能量的效率,以降低數據中心電費和冷卻成本。隨著電路板溫度接近100oC,服務器機箱也變得越來越熱。設計周期越來越短,但是,視裕度測試結果的不同而不同,同時為了滿足不同市場及客戶的獨特需求,設計方案在最后一分鐘仍然需要各種修改。對于有多個電源的電路板,排序一直是一種常見要求,但是這種要求變得越來越復雜了,因為電源數量多達 20 至50個,而且跨越了多種功率域。

迄今為止的解決方案

諸如排序、監控、監視和裕度調節等電源管理任務一直由一堆雜亂無章的組件完成,包括監察器、排序器、ADC、DAC、放大器和微控制器。使這些分立器件協調一致地工作占據了大部分設計時間。集成型解決方案源于具有用于裕度調節、ADC 監視和 EEPROM 故障記錄之附加功能的監控器和排序器。但是這些器件在修整、裕度調節和監視方面的電壓準確度欠佳。另外還有片內系統 (SoC) 器件,此類器件集成了許多獨立的數字門和具有 ADC、DAC、比較器及 PWM 輸出的邏輯電路。由于不具備任何的電源管理架構,因此即使面對最基本的任務,這些器件也需要進行大量的編程,從而耗費長達數月的時間來完成設計和驗證工作。

由于人們竭力推進電源系統的數字化管理,因此產生了各種數字電源解決方案,這些解決方案的DC/DC 轉換器環路采用了ADC、數字補償器和數字 PWM。由于這種采樣系統固有的量化,數字環路在電源輸出電壓中產生了更大的噪聲和紋波。而且,這類系統往往有較慢的瞬態響應、準確度欠佳甚至可能出現不規律、不可預期的運行表現。而另一方面,模擬環路速度更快、噪聲更低、更可預測。管理多個電源時,需要對POL電源進行數字化配置以及與其進行數字化通信,但是電源環路本身依然可以保持是模擬的,這樣就可以同時充分利用模擬和數字技術的優勢。

完整解決方案

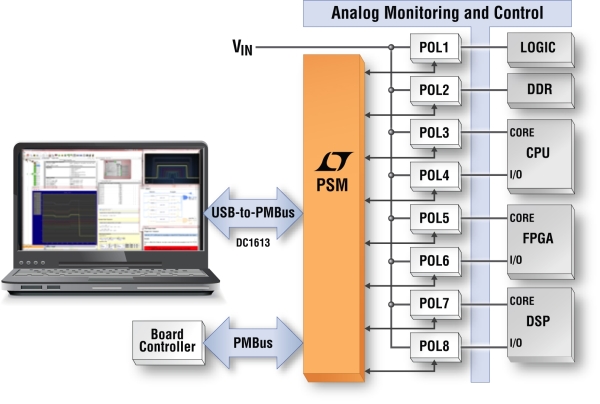

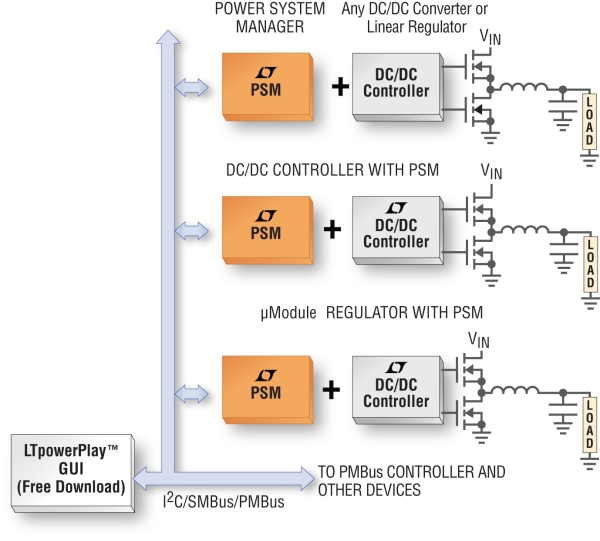

凌力爾特一直牢記POL電源發展趨勢,已經從頭開始設計了一種完整的數字電源系統管理(DPSM) 解決方案。其核心理念就是,電源環路依然保持是模擬的,同時增加數字接口和數字控制。該解決方案如圖1所示。這個DPSM 系列包括多種可互操作的器件,有的有內置DC/DC轉換,有的則沒有,如圖2所示。所有這些器件都通過業界標準PMBus接口與電路板上的控制器通信。選擇PMBus可實現固件重用,有助于節省設計時間。對于那些首選自主工作而無需開發代碼的工程師,凌力爾特還提供工程級開發軟件LTpowerPlay,以定制器件配置。

圖1:凌力爾特的DPSM架構。POL電源仍然保持是模擬的,同時增加了數字通信及數字控制。

(Analog Monitoring and Control:模擬監視與控制;USB-to-PMBus:USB 至 PMBus;Board Controller:電路板控制器;LOGIC:邏輯電路。)

圖2:凌力爾特DPSM器件類型,視所控制的電源軌數量的不同而不同,每一類都提供多款器件。

評論