基于FPGA的M2M異構虛擬化系統(一)

如圖 14,在團隊自主研發的QS-I 硬件系統的基礎上,團隊開發了函數系統庫和多個應用程序。其中系統函數庫包括圖形庫、VGA顯示器接口、RS232串口接口、PS/2鍵盤接口。應用程序根據所最終運行時的機器碼可以分為MIPS體系結構應用程序和x86體系結構應用程序。其中,MIPS體系結構應用程序包括使用MIPS匯編語言編寫的俄羅斯方塊游戲和使用C語言編寫的吃豆子游戲;x86體系結構應用程序包括使用8086匯編語言編寫的推箱子游戲。

該項目的硬件系統是自主研發的,因而需要開發基于該系統的軟硬件接口函數庫,并且需要編寫應用程序測試系統的各種功能。

該項目的硬件系統支持MIPS體系結構的指令集。基于MIPS指令集,團隊開發了將MIPS匯編語言翻譯成機器碼的匯編程序,并分別使用MIPS匯編語言和C語言開發了系統函數庫。使用MIPS匯編語言開發應用程序,用來驗證五級流水線CPU的功能正確性,檢測出數據相關和控制相關出現的問題,驗證硬件系統對MIPS指令集的支持度,驗證CPU與各種外部設備互聯的正確性以及系統的總體性能。

基于MIPS匯編語言開發了俄羅斯方塊游戲。俄羅斯方塊的基本規則是移動、旋轉和擺放游戲自動輸出的各種方塊,使之排列成完整的一行或多行并且消除得分。本設計的俄羅斯方塊有5種基本形狀,7種顏色;可通過鍵盤控制左移(A)、右移(D)、旋轉(W)、加速下降(S)、暫停(Space)、退出(Q)、選擇級別(L);游戲設置兩種級別,普通下降速度和較快下降速度兩級;游戲界面顯示幫助、玩家所得分數、下一個即將下落的形狀等信息;當方塊到達頂端時,游戲失敗;玩家通過不斷的刷新最高分獲得愉悅。

為了提高軟件開發的效率,使軟件開發人員方便的使用硬件系統及其外設資源,團隊使用Gcc編譯器和MASM匯編器的組合,項目團隊開發了基于C語言的應用程序,驗證硬件系統對Gcc編譯器和MASM匯編器生成的機器指令的支持。團隊還開發了基于C語言的系統函數庫,包括圖形庫、VGA顯示器接口、鍵盤接口和串口接口等。此外,團隊還使用JAVA語言,開發了MIPS指令CPU模擬器,使得在軟件的開發過程中不需要每次都傳輸到硬件開發板上就可以進行調試,大大提高程序開發的效率。

基于C語言開發了吃豆子游戲。吃豆子的基本規則是控制packman的移動,使之吃完所有的豆子,并且躲開怪物的追捕。本程序設計的怪物有2個;豆子有兩種,一種普通的小豆子,還有一種大豆子,吃了大豆子能讓怪物慢下來幾秒鐘;可通過鍵盤控制左移(A)、右移(D)、旋轉(W)、加速下降(S)、暫停(Space)、退出(Q);游戲界面顯示幫助、玩家所得分數等信息;當玩家被怪物抓到時,游戲失敗;玩家將所有的豆子都吃光時,游戲正常結束。

該硬件系統能夠執行不同指令集體系結構的機器碼。為了驗證系統執行不同指令集機器碼的正確性,調試出硬件系統中存在的問題,團隊開發了基于x86匯編語言的應用程序。團隊還開發了基于x86語言的系統函數庫,包括圖形庫、VGA顯示器接口、鍵盤接口和串口接口等。

基于x86匯編語言開發了推箱子游戲。推箱子的基本規則是控制機器人的移動,使之把所有的箱子放到指定的位置。箱子只有1種;可通過鍵盤控制左移(A)、右移(D)、旋轉(W)、加速下降(S)、暫停(Space)、退出(Q);游戲界面顯示幫助、玩家所用的時間等信息;玩家將所有的箱子都放到適當的位置時,游戲正常結束。

4.詳細設計方案

4.1.RISC CPU詳細設計方案

4.1.1.RISC CPU(QS-I)整體模塊

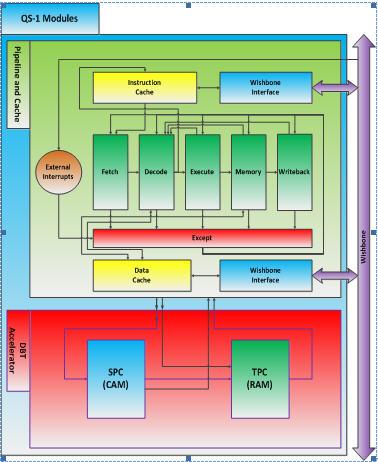

圖 15 QS-I CPU整體模塊圖

如圖 15所示,QS-I的整體模塊中主要包括兩部分,第一部分是五級流水線和Cache,另一個模塊是動態二進制翻譯加速模塊(DBT Accelerator)。CPU的對外接口符合Wishbone總線標準。

在下一節中,我們將會介紹QS-I CPU中各個單元模塊功能以及其時序。

4.1.2.RISC CPU(QS-I)各單元模塊功能與時序

4.1.2.1五級流水線模塊詳細設計方案

功能描述

本模塊的功能是完成指令的五級流水化執行,并支持中斷及異常。一條指令的執行經過是Fetch(取指) à Decode(譯碼) à Execute(執行) à Memory(訪存) à Writeback(寫回)五個階段。其中Fetch階段從指令Cache中由PC(Praogram Counter)取得下一條指令;Decode階段完成指令的大部分譯碼工作,并產生相應的控制信號;Execute階段主要完成指令的算術運算以及少量選擇電路;Memory階段完成訪存任務,數據將從數據Cache中讀取或者寫入;Writeback階段完成寫回指令的修改Register File(寄存器堆)的寫操作。此外,本模塊完成了流水線中的精確中斷處理。

- 子模塊列表

Module | Description |

pc_reg | Module of PC register |

if_stage | Instruction Fetch stage |

if_id_reg | Registers between IF and ID stages |

id_stage | Instruction Decode stage |

id_exe_stage | Registers between ID and EXE stages |

exe_stage | Execute stage |

exe_mem_reg | Registers between EXE and MEM stages |

mem_stage | Memory stage |

mem_wb_reg | Registers between MEM and WB stages |

wb_stage | Writeback stage |

except | Module of exception handling |

詳細設計

pc_reg

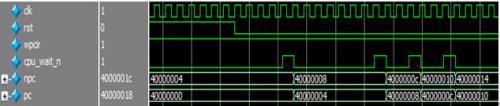

本模塊完成對PC寄存器的更新任務。若流水線中出現stall或者Cache發生miss等情況則延遲對PC寄存器的更新。本模塊的時序如下圖所示。

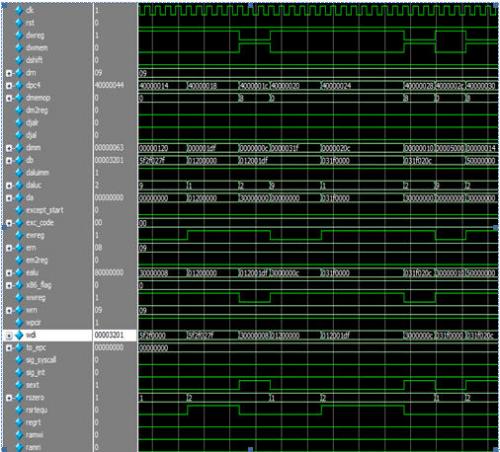

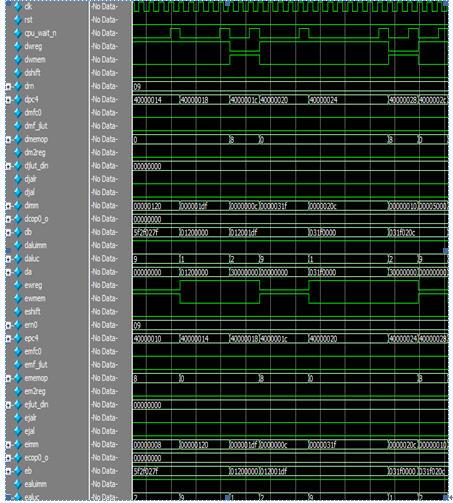

圖 16 pc_reg時序圖

if_stage

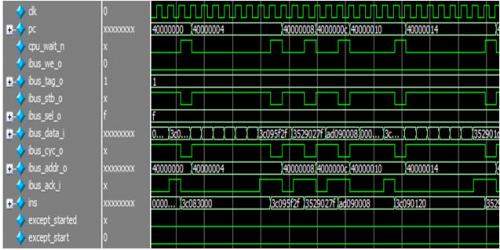

本模塊完成對指令Cache的取指。模塊的對外接口符合Wishbone總線標準。CPU的對外接口包括IBus(指令總線)和DBus(數據總線),為了將CPU成功集成入Wishbone總線中,CPU的對外接口部分的邏輯設計必須符合Wishbone標準。此外,CPU對外部設備(如RAM,ROM,UART)的訪問速度以及CPU有無Cache(高速緩存)是未知的,因此這部分的邏輯設計必須帶有通用性。

本模塊的主要時序如下圖。

圖 17 if_stage時序圖

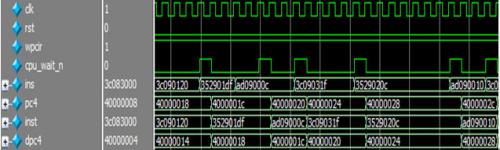

if_id_reg

本模塊完成IF和ID兩個階段之間的信號流水。本模塊的時序圖如下。

圖 18 if_id_reg時序圖

id_stage

本模塊完成指令的基本譯碼,并產生相應的控制信號。RISC處理器的結構競爭、控制競爭、數據競爭三大競爭的解決:

采用旁路(bypass)技術解決數據競爭,雙跳(double bump)解決結構競爭,延時槽技術解決控制競爭。

本模塊的基本時序圖如下。

圖 19 id_stage時序圖

id_exe_stage

本模塊完成IF和ID兩個階段之間的信號流水。本模塊的時序圖如下。

圖 20 id_exe_reg時序圖

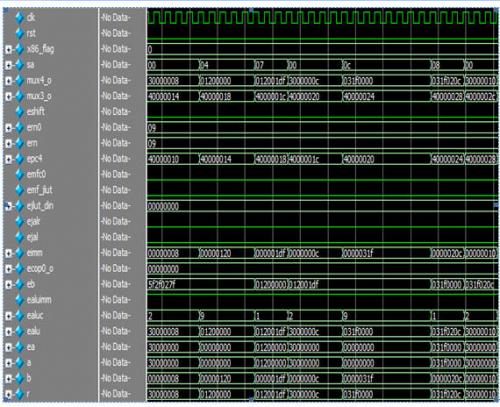

exe_stage

本模塊完成指令的算術邏輯運算。其中,運算包括add, sub, and, or, xor, nor, sll, srl, sra, lui等算術或邏輯運算。

為了x86架構動態翻譯的加速需要,在ALU(算術運算單元)中增加了x86 flag標志寄存器,并將該寄存器作為一個系統寄存器,用戶程序可通過mfc0,mtc0指令來修改flag標志寄存器。

本模塊的時序圖如下。

圖 21 exe_stage時序圖

評論