基于FPGA的M2M異構虛擬化系統(一)

摘要

本文引用地址:http://www.104case.com/article/201809/388223.htm在多核體系構架與并行計算時代,尤其是云計算的出現,虛擬化技術正迅速發展成為計算系統中的一項核心技術。虛擬化技術提供了系統層次之間的抽象化,并將資源以一個或多個虛擬的運行環境提供給用戶。目前對虛擬化的研究工作主要關注于資源的分割,獨立和封裝等研究點,但主要在一個特定處理器體系結構以及處理器同構的前提下。

本項目提出一種新穎的M2M(Multiple ISAs applications to Multiple heter-ogeneous core,M2M)概念,將虛擬化系統分為多核異構層、虛擬化管理層、二進制翻譯層、軟件應用層四個層次,創新地在傳統的虛擬化管理層上增加二進制翻譯層,從而引入多個不同體系結構的應用程序,虛擬化管理器調度分配給硬件層引入的異構處理器。M2M的特性使虛擬化系統上層應用的靈活性大大增加,并且硬件異構化也使系統的效率有效提升。

本項目主要貢獻點和創新點有:

多指令集體系應用虛擬環境。在應用層提供不同指令集體系構架的虛擬運行環境,以支持不同應用系統的應用程序。

軟硬協同的二進制翻譯層。在二進制翻譯層,采用軟硬協同的方式實現不同架構體系間的動態二進制翻譯,提高硬件目標代碼生成和運行的性能和靈活性。

設計實現了自主可擴展32位的SoC核。在多核異構層,設計了一個自主,可擴展,可配置的32位RISC處理器。基于此處理器核可配置實現多個RISC SoC平臺(QS-I)。本項目在XUP Virtex-5和Digilent Nexys3 FPGA開發平臺構建了多核異構層。

動態虛擬化管理。在虛擬化管理層,以輕量級的方式實現了系統資源與上層應用的管理。通過資源管理與任務調度動態分配或遷移運行任務。虛擬層的多個體系結構的應用程序(如x86和MIPS)可動態運行于異構的處理器核上(如處理能力不同的MIPS核)。

提供了系統庫和運行程序。在軟件應用層,為自主設計的QS-I平臺提供完善的程序運行環境并設計了多樣化的應用程序。項目完全自主地設計實現了系統庫(如圖形庫、I/O庫)以及典型的多樣化應用軟件,包括MIPS下的吃豆子游戲、X86下的推箱子游戲。

1.項目背景

在計算機科學領域中,虛擬化代表著對計算資源的抽象,而不僅僅局限于虛擬機的概念,實現虛擬化的方法不止一種,無論何種方法都是以不同層次的抽象來實現某一視角對應的效果。

1.1.項目需求

虛擬化技術正迅速發展成為計算系統中的一項核心技術,它提供了計算機系統層次之間的抽象層,并將資源分配以提供一個或多個虛擬的運行環境。現在對虛擬化的研究工作主要關注于資源的分割,獨立和封裝等研究點,但主要在一個特定處理器體系結構以及處理器同構的前提下。本項目提出一種新穎的M2M(Multiple ISAs applications to Multiple heterogeneous core,M2M)概念,將虛擬化系統分為多核異構層、虛擬化管理層、二進制翻譯層、軟件應用層四個層次,創新地在傳統的虛擬化管理層上增加二進制翻譯層,從而引入多個不同體系結構的應用程序,并在硬件層引入處理器的異構性。M2M的特性使虛擬化系統的上層應用的靈活性大大增加,并且硬件異構化也使系統的效率有效提升。

1.2.相關技術及其發展現狀

本小節將介紹虛擬化以及動態翻譯等技術的基本概念及其發展現狀。

1.2.1.虛擬化技術的基本概念

虛擬化技術最早可以追溯到上個世紀60年代,IBM公司的System 360系統對運行多個虛擬化系統進行了最早的嘗試。如今,虛擬化技術正迅速發展成為計算機系統中的一項核心技術,它提供了計算機系統層次之間的抽象層,并將資源分配以提供一個或多個虛擬的運行環境。

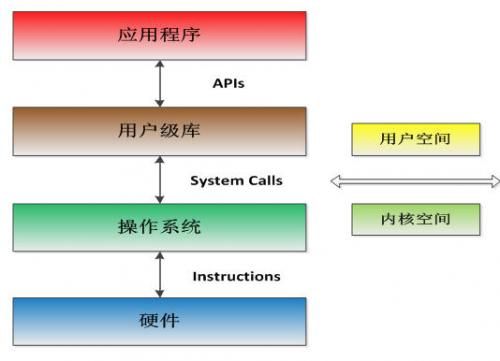

例如計算機系統可分為如圖 1中所示的四個層次,由最底層的硬件自下而上分別是操作系統、用戶庫、應用程序。相應地,虛擬化技術可以針對各個層次進行抽象虛擬,從而為上一層的應用提供一個或多個虛擬環境。

圖 1 計算機系統的四個層次

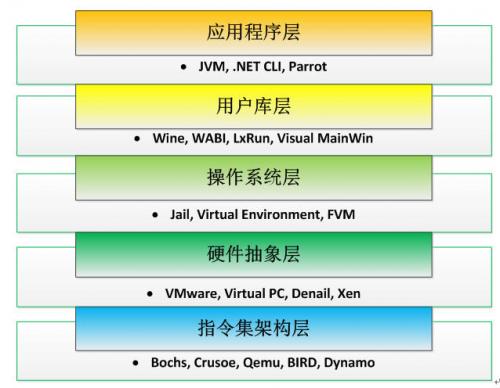

更具體地,虛擬化的層次可分為如圖 2所示的指令集架構(ISA)、硬件抽象層(HAL)、操作系統、用戶級庫、應用程序的五個層次。圖 2中還在各個層次下方列出了與其對應的知名產品。

圖 2 虛擬化技術的五個層次及其相應產品

1.2.2.ISA層的虛擬化技術

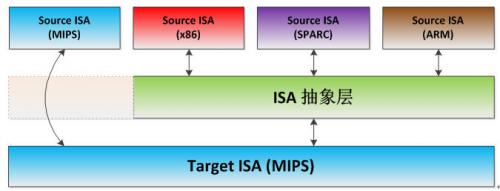

ISA層的虛擬化是虛擬化技術中的一個重要內容,它的主要目的是為上層應用提供一個或多個不同于物理層實際處理器ISA的ISA抽象層,從而使得多個處理器架構的應用程序能夠在同一個處理器上運行,如圖 3所示。

圖 3 ISA層的虛擬化

ISA層虛擬化所產生的異構性使處理器本身的性能得到提高[1]。同時,x86架構憑借其強大的軟硬件支持,仍將在未來的處理器競爭中占有統治地位[2] 。本項目將重點實現不同ISA(x86和MIPS)之間的虛擬化技術,使該RISC處理器與x86架構達到二進制兼容。

1.2.3.動態翻譯技術

在ISA層的虛擬化中,二進制翻譯是最重要的實現技術。二進制翻譯是指把一中體系結構的機器碼翻譯成為另一種體系結構的機器碼。通過二進制翻譯,體系結構將成為一個軟件層,它使得復雜的遺留體系結構能夠用簡單的硬件來實現,并且使得新穎的體系結構能夠兼容原來的軟件;此外,二進制翻譯能夠促進軟件的優化[3]。

二進制翻譯有兩種主要的實現方法,一種是靜態翻譯,另一種動態翻譯。

靜態翻譯把整個二進制可執行文件翻譯成目標體系結構的指令集,它不需要先運行代碼,所有的翻譯都在編譯時完成。所以靜態翻譯很難做到正確性,因為不是所有的代碼都能在編譯時被翻譯器發現。比如,可執行文件的某些部分只能通過間接跳轉才能到達,而間接跳轉的目標值只有在運行時才知道。

動態翻譯把一小段源體系結構的代碼翻譯成目標體系結構的代碼并把這一小段生成的代碼緩存起來。只有當代碼被運行時才開始執行翻譯。跳轉指令會被指定到已經翻譯和緩存起來的代碼段上。

2.項目目標及開發平臺選擇

2.1.項目目標及內容

本項目提出一種新穎的M2M(Multiple ISAs applications to Multiple heter-ogeneous core,M2M)概念,在虛擬化管理層上增加二進制翻譯層,從而引入多個不同體系結構的應用程序,并在硬件層引入處理器的異構性。如圖 4所示的項目總體層次包括多核異構層、虛擬化管理層、二進制翻譯層以及軟件應用層。

圖 4 項目總體層次

本項目目標是基于Xilinx公司的XUP Virtex-5和Digilent的Nexys3 FPGA開發板實現多個RISC SoC平臺建立硬件多核異構層;選擇MIPS和x86 ISA構架設計吃豆子、俄羅斯方塊等典型應用程序構成多樣化應用場景,實現M2M原型系統。

具體任務如下:

多核異構層

實現MIPS基本指令集,支持精確中斷,含一級Cache的32位RISC CPU的RTL描述及其驗證;

完成VGA(或DVI)、PS/2、SRAM、UART等外設的控制器模塊描述及各個模塊的驗證;

引入Wishbone總線,集成SoC平臺的各個模塊;

基于不同FPGA的RISC SoC平臺(分別在XUP Vritex-5和Digilent Nexys3上基于自主軟核QS-I搭建了RISC SoC平臺),構建多核異構層

虛擬化管理層

對多核異構層的資源管理;

對應用層多樣化程序的調度分配

二進制翻譯層

以軟硬件協同方式完成RISC處理器在ISA層對x86的虛擬化,使得RISC處理器能夠與多架構(如x86)二進制兼容;

動態翻譯的軟件架構設計

軟件應用層

系統軟件編寫。系統軟件包括外設的驅動程序及系統控制程序;

運行環境及庫編寫。設計實現系統庫(如圖形庫、I/O庫);

應用軟件編寫。應用軟件包括多個SoC完整應用系統(x86和MIPS),如簡單的游戲程序。

2.2.開發平臺選擇

本項目主要選用Xilinx公司的XUP Virtex-5開發平臺及Digilent公司的Nexys3開發平臺。

2.2.1.XUP Virtex-5 FPGA開發平臺簡介

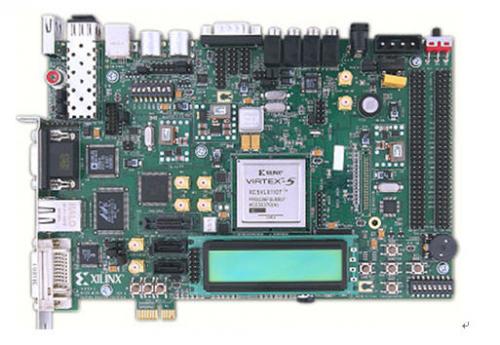

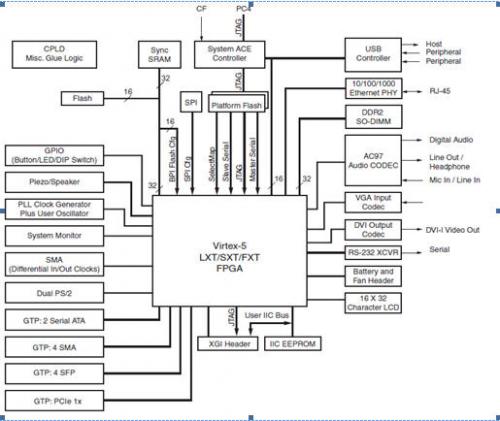

XUP Virtex5是集成了OpenSparcT1開源微處理器的一個強大系統。其豐富的特色以及開發平臺的通用性,使得該板卡非常適合在教學及研究的領域搭建各種系統。如數字設計、嵌入式系統、通訊系統、網絡、視頻及圖像處理等各個領域。XUP Virtex-5實體圖見圖 5,其資源模塊圖如圖 6所示。XUP Virtex-5含有豐富的片上資源以及完整的工業標準接口。

圖 5 XUP Virtex-5 FPGA開發平臺

圖 6 XUP Virtex-5平臺資源模塊

本項目基于XUP Virtex-5 FPGA開發平臺構建了基于自主軟核QS-I的RISC SoC平臺。

2.2.2.Digilent Nexys3 FPGA開發平臺簡介

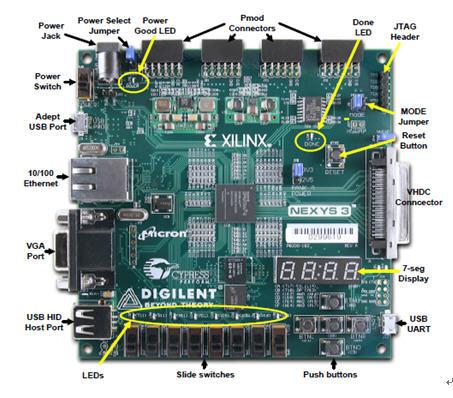

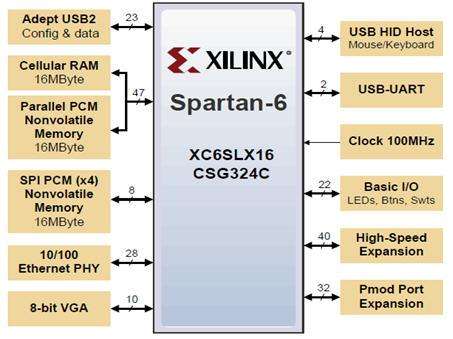

Digilent公司的Nexys3平臺是一個基于Xilinx Sparten-6 FPGA的完整,易用的數字電路開發平臺。Sparten-6 FPGA為高性能邏輯設計做了充分優化,其片內的block RAM,時鐘管理模塊,DSP等資源為高級邏輯設計提供了必要硬件基礎。Nexys3實體圖見圖 7,其平臺資源模塊如圖 8。

圖 7 Digilent Nexys3 FPGA開發平臺

圖 8 Digilent Nexys3平臺資源模塊

評論