使用多通道體系結構優化LPDDR4的性能和功耗

LPDDR4是用于移動應用的最新雙數據率同步DRAM,它是當今高端便攜產品中常見的DRAM類型,應用于如Samsung Galaxy S6智能手機,Apple iPhone 6S [1],以及數種最新發布的設備。除了移動應用之外,預計LPDDR4會像其前任LPDDR3那樣應用于平板電腦、輕薄筆記本電腦中,會采用“底層存儲器”配置,亦即,DRAM以物理方式焊接在主板上。

本文引用地址:http://www.104case.com/article/201808/385960.htmLPDDR4在很小的PCB面積和體積上提供了巨大的帶寬;在3200Mbps的數據率下,當兩片Die封裝在一起時,單個15毫米x15毫米LPDDR4封裝包可提供25.6 GByte/s的帶寬。LPDDR4建立在LPDDR2和LPDDR3的成功基礎之上,增加了新的特性并引入了主要的結構變化。

本白皮書中闡明了LPDDR4與以前所有JEDEC DRAM規格的差異之處。討論了下述方面:

設計人員為何選擇LPDDR4

LPDDR4體系結構的亮點

如何最好地配置LPDDR4通道

如何處理具有多通道連接的2片和4片封裝

通過系統級芯片(SOC)分割共享通道的優點

如何優化通道以實現最低功耗

為什么是LPDDR4?

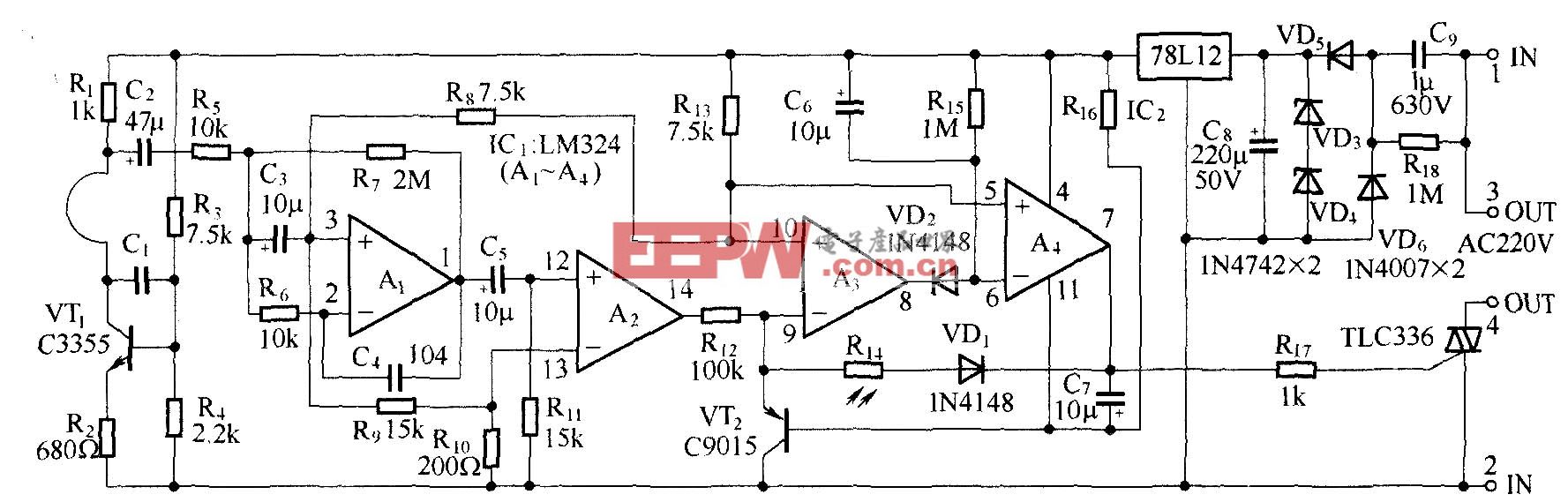

LPDDR4包含多項特性,這使得SOC設計團隊能夠降低分離DRAM的功耗。對于諸如PC和服務器等桌面設備,通常將使用安裝在雙列直插內存模塊(DIMM)上的DDR器件,所述DIMM位于64位寬總線上。這類板級解決方案能夠就地升級DRAM容量,但需要長且負載較重的連接線,與較短的走線相比,它消耗的功率更高。對于使用LPDDR2、LPDDR3和LPDDR4的系統,每條總線上的內存器件通常數量更少,連接線也更短,因而消耗的功率比DDR2、DDR3和DDR4器件更低。

設計團隊能夠調用LPDDR4 DRAM內的節能選項。這些特性包括更低的電壓和I/O電容;更小寬度的多路復用命令和地址總線;消除了on-DRAM DLL;更快進出的低功耗待機模式;更快、更加簡單的變頻。

最后,LPDDR4 DRAM具有溫度感知刷新特性,這有助于使DRAM的刷新率與DRAM的位單元本身的要求匹配,尤其是在低功率自刷新待機模式下更是如此。在待機模式下可自動啟用該特性,類似地,在主動模式下可讀取溫度指示,使得LPDDR4控制器能夠調節其自刷新率,從而與LPDDR4器件的熱狀態相符。

LPDDR4采用了針對移動裝置的模型

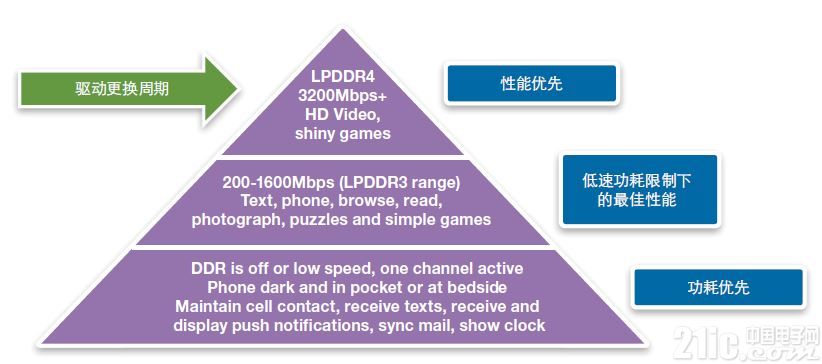

在實際應用中,移動用戶僅在較少的時間段內才會用到LPDDR4的最高工作頻率。此時,用戶或是采集或顯示高清晰(4K)視頻,或是玩具有高圖形要求的游戲,或是處理圖形,或是引導或加載新的軟件。

在部分時間段內,內存會降至LPDDR3速度級別。這一性能水平足以支持文本、呼叫、網頁瀏覽、照片、簡單游戲:所有這些功能對CPU或GPU沒過高要求。

在大部分時間段內,移動設備并不使用,它或是在口袋內、或是在床邊,此時DRAM斷電或處于低速模式下。僅一個內存通道處于活動狀態下,用于執行“始終在線、始終連接”任務。在該模式下,設備執行后臺任務,如保持電池接觸,接收消息,接收/顯示推送通知,郵件同步,以及時間顯示。

然而,正是由于最高使用時間的設備性能,很多移動用戶升級了其設備,這正是該使用模式下優秀用戶體驗十分重要的原因之所在(圖1)。

圖1:最高使用時間是移動用戶升級循環的驅動因素

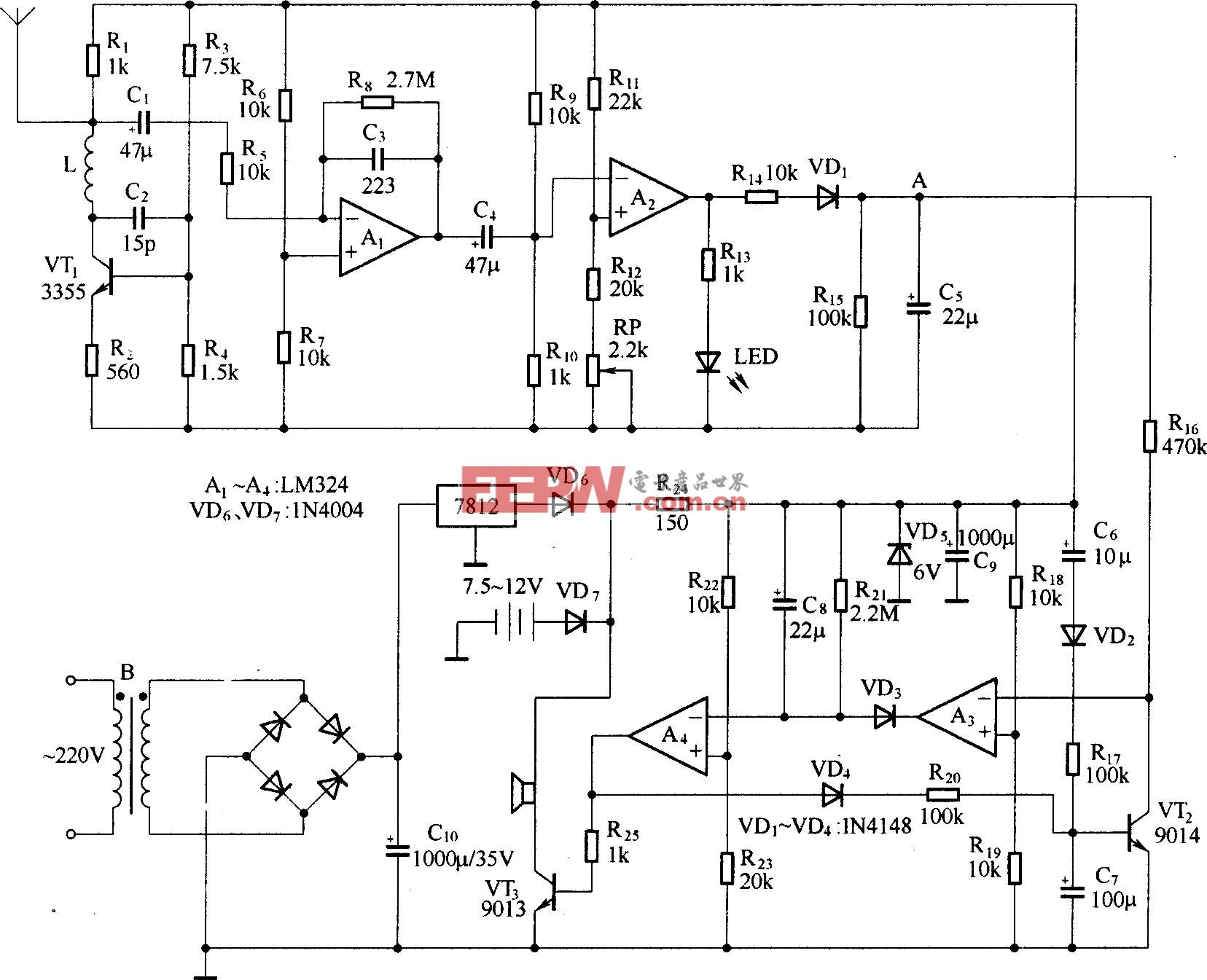

LPDDR4體系結構變化

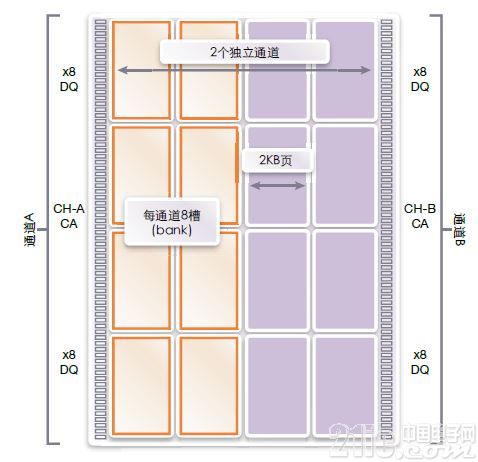

與前代相比,LPDDR4規范中確定了多種性能和特性改進。最為重要的是,LPDDR4對體系結構進行了重大改變:LPDDR4器件采用了每一裸片上2個獨立通道的布局方案。

DDR2、DDR3和DDR4器件的每一封裝包提供了一套命令地址輸入總線和一套數據總線,最為常見的是每一封裝包一個裸片。LPDDR2和LPDDR3的每一封裝包可提供1~4個裸片。對于LPDDR4、LPDDR3和LPDDR2,在雙裸片和4裸片封裝包情形下,通常提供了2套獨立的命令地址輸入和數據總線(通道)。換句話講,LPDDR2和LPDDR3器件實施了部分多通道,其中,每一封裝包提供了2個獨立通道。LPDDR4將該特性發揮到極致,這是因為每一裸片都有兩個獨立通道,大多數封裝包都有4個通道。

連接多個通道

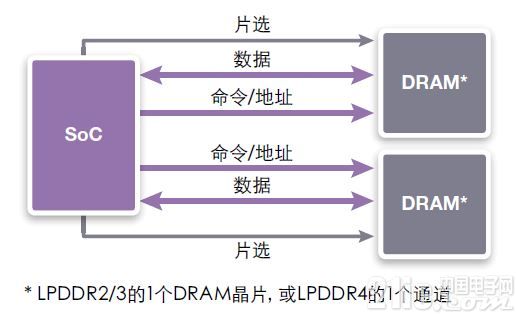

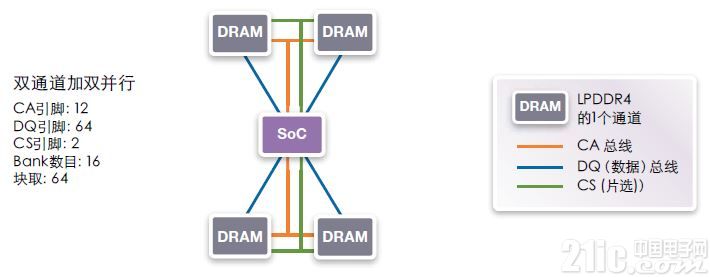

LPDDR4體系結構天然具有2個通道(圖2),每一裸片有2套命令地址輸入和2套數據總線。LPDDR4的2裸片封裝包提供了4個獨立通道。為了更有效地使用LPDDR4,設計人員必須理解LPDDR4體系結構變化對SoC體系結構的影響。

圖2:LPDDR4雙通道體系結構

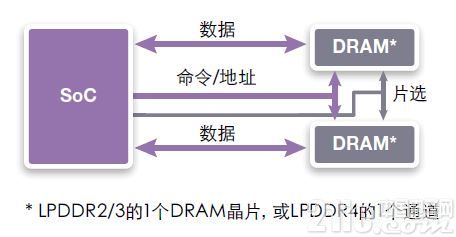

對于具有1個通道(如LPDDR3的單裸片封裝包)的單個DRAM器件,只能做單向連接,即SOC上的命令/地址總線接到位于DRAM上的命令/地址總線,SOC數據總線接到DRAM數據總線(圖3)。片選(CS)可在需要時使能DRAM。

圖3:連接單個DRAM裝置的標準方式

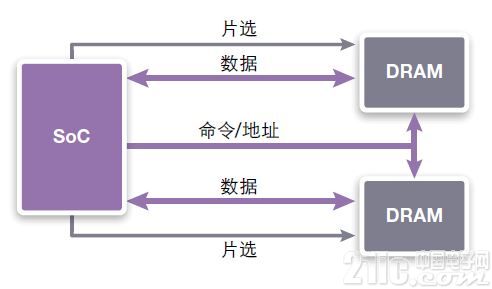

2個DRAM器件,或具有2個獨立接口的單個DRAM器件(如LPDDR4)可支持4種可能配置:

并行(前后緊接)

串行(多級)

多通道

共享命令/地址

并行(前后緊接)連接

對于在DDR2/DDR3/DDR4方面具有豐富經驗的設計人員,最熟悉的選擇是并行或前后緊接配置。并行配置(圖4)對于2個或多個DRAM裸片是恰當的,對于與同一命令/地址總線相連的LPDDR4的2個通道也是恰當的。它們采用了相同的片選,但每一數據總線具有獨立的數據通道。在這類并行連接中,所有的DRAM器件接收相同的命令和地址,但會通過不同的字節線發送其數據。由于可同時訪問所有器件,因此兩個DRAM始終處于相同狀態。它們打開相同的內存頁面,并訪問相同的數據列,但保存在每一 DRAM中的數據不同。

圖4:并行(前后緊接)連接

串行(多級)連接

第二種選擇是采用串行或多級配置將器件連接在一起(圖5)。這等效于將多個DIMM置于PC上的同一通道內。命令/地址和數據總線均連接在兩個DRAM器件上,但根據命令循環選中的2個不同的片選,以對兩個DRAM器件的訪問進行獨立控制。這兩個器件可處于不同狀態,具有不同的活動內存頁面。典型情況下,SOC負責控制共享數據總線,確保DRAM不會同時進行數據傳輸。

圖5:串行(多級)連接

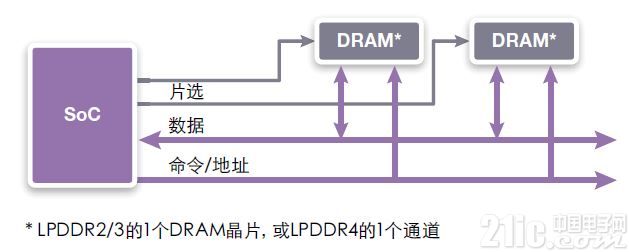

多通道連接

多通道連接(圖6)為DRAM的每一通道或每一DRAM器件提供了與SOC的獨立連接,其中,每一器件或通道具有自己的命令/地址總線,數據總線和片選。由于采用了這一靈活配置,每一DRAM器件(或器件組)能夠彼此完全獨立地工作。它們可能處于不同狀態,接收不同命令和不同地址,當一器件執行寫入操作時,另一器件可執行讀取操作。

多通道連接還允許DRAM工作在不同功耗狀態下。例如,某一塊內存可能處于待機自刷新模式,而另一內存處于完全激活狀態。

圖6:多通道連接

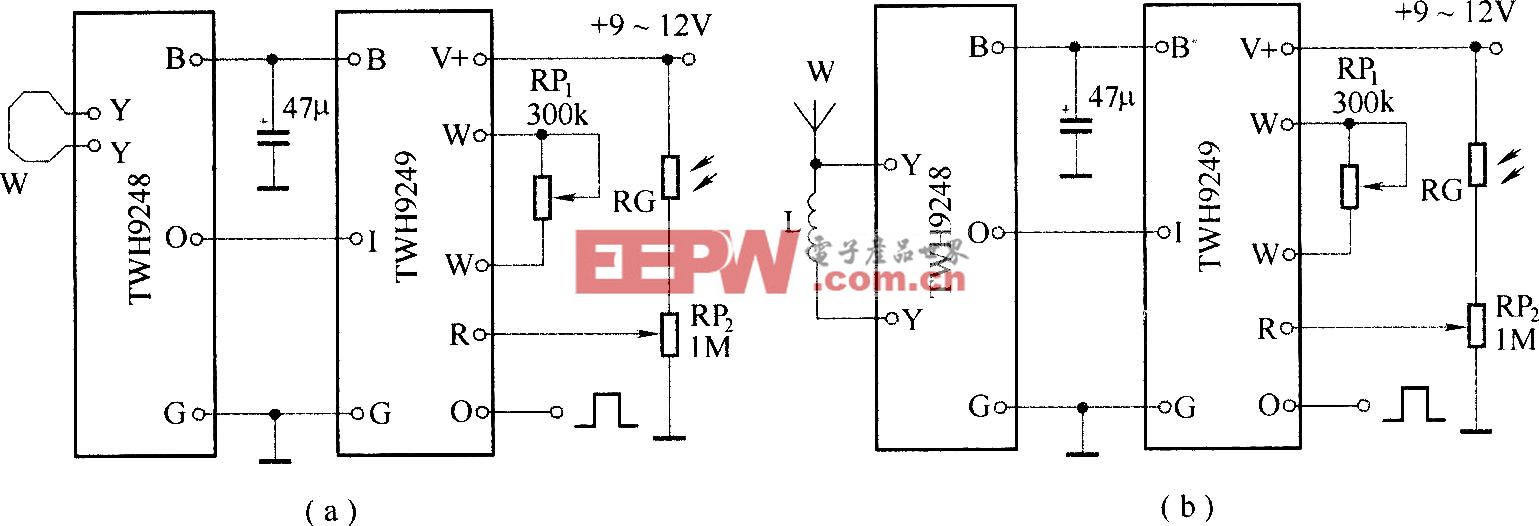

共享命令/地址(CA)連接

最后一種配置選擇更常應用在非低功耗DDR器件中,這是一種具有共享命令/地址(CA)或共享AC(圖7)的多通道配置。在該配置下,兩個DRAM裝置接收相同的命令和地址,與串行連接類似,片選決定了哪個DRAM器件負責監聽特定的時鐘周期,因而每一器件可能處于不同狀態下。兩個通道之間的DRAM命令仲裁在SoC內部完成,但每一DRAM能夠獨立傳輸數據。

圖7:共享CA連接

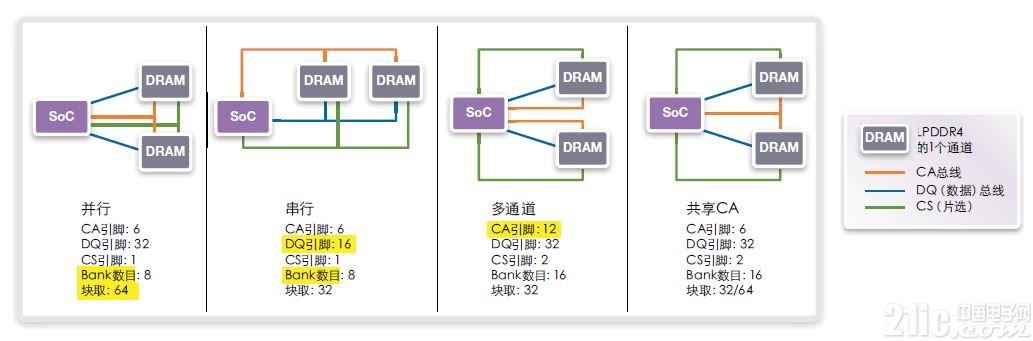

雙通道連接的各種配置選項的比較

這些配置選項中的每一個各有其優缺點(圖8)。例如,并行實施僅有8個可用庫(bank),任一時刻在32位數據總線上可突發塊取的最小數據量為64字節。并行方法不太適合于使用堆疊封裝(POP)的設計。

圖8:LPDDR4的雙通道(1個晶片)連接選項比較

串行連接也不太適合于POP實現。它的確能節省一些DQ引腳,但由于DRAM器件共享了數據總線,它所提供的帶寬只有其他解決方案的一半,該方法的吸引力較低。

共享CA適合于DDR系統,多通道連接使得設計團隊能夠從LPDDR4中獲取最大好處。

管理具有多通道連接的2裸片和4裸片封裝包

在LPDDR4的實施中,最常見的方式是在單個封裝包中使用2個LPDDR4裸片,該包提供了4個16位通道,可實現8種不同拓撲方案。在將LPDDR4器件連接至SOC的8種可能方式中,有三種特別有用的實施方案:

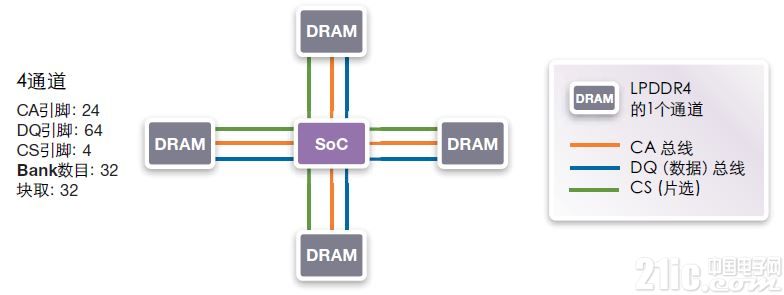

“真正”的4通道,雙通道加雙并行,完全并行

對于希望在其LPDDR4裝置中實現最大帶寬的設計團隊,尤其是在使用較小的數據塊傳輸時,可能會考慮真正的4通道實施方案(圖9)。與其他實施方案相比,它具有最大的bank數目,以及最小的塊提取尺寸。它要求在SOC上具有24個CA引腳,可與SOC上的4個單獨的內存控制器以及PHY一起實施。

圖9:真正的4通道實施

雙通道加雙并行實施在全并行實施和4通道實施之間實現了良好折衷。對于LPDDR3-LPDDR4組合(圖10),它尤其有用。在使用LPDDR4的早期商用SOC中,大部分都采用了該配置。

雙通道加雙并行

圖10:雙通道和并行實施

全并行實施僅采用了6個CA引腳,具有最大的DQ數(64)。然而該系統中僅提供了8個Bank。最小尺寸塊提取尺寸為128字節,這將會限制其在某些應用中的實用性。由于總線負載或芯片級時序收斂方面的原因,可能還需要復制CA總線。

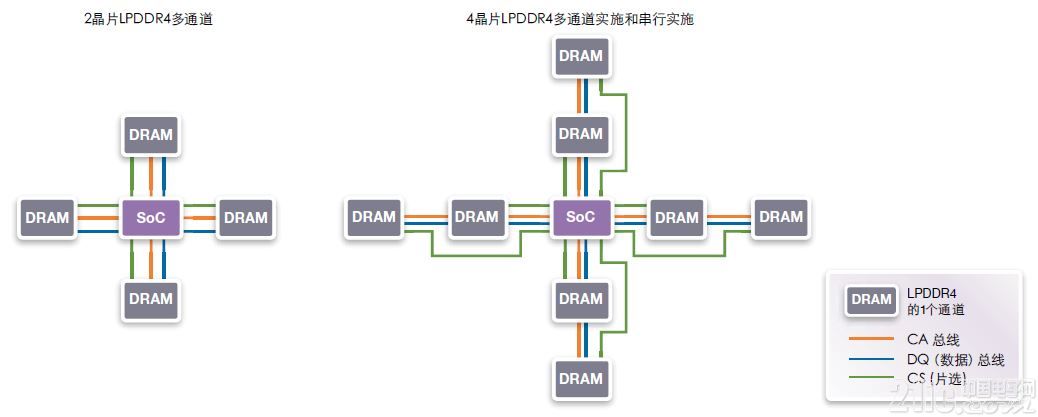

圖11顯示了雙裸片4通道LPDDR4多通道實施(左側)和4裸片實施(右側)的示例。LPDDR4封裝包具有4個連接的裸片,每一物理通道具有與其相連的2排(rank)內存存儲體。對于該配置,要求設計團隊在包的4個通道的每一通道的串行方向上擴展連接。不幸的是,4裸片包未提供8通道連通性;在4裸片包上只有4個通道。

圖11:雙裸片和4裸片實施。4裸片LPDDR4多通道和串行實施增加了DRAM容量。該解決方案與2裸片封裝包兼容

概括而言,推薦的雙裸片LPDDR4實施為:

雙通道加并行,這是LPDDR3用戶最熟悉的方案,也是可以實現LPDDR3/LPDDR4組合的實現方式;

4通道,這是最靈活并具有潛在最高性能的方案。

關于共享通道的設計推薦,通過多Bank改善LPDDR4的性能

類似地,LPDDR4繼承了DRAM的很多特性,其存儲結構由Bank構成,每一Bank具有多行(Row),每一行具有用于存儲數據的多個列(Column)。訪問位于相同行內保存在列中的數據很快,訪問位于不同Bank內不同的行也很快,但訪問位于相同Bank內的不同行則會很慢。

獨立訪問其他器件的每一通道意味著,每一通道上的每一Bank可以具有不同的活動行。對于像視頻和網絡包等在內存中隨機分布的小尺寸的數據傳輸類型而言,擁有更多的Bank能夠避免一些固有的、會限制性能的內存時序參數。在盡可能多的Bank上傳輸數據能夠改善性能是因為它能降低遇到一些內存時序參數的概率。

在系統中有更多的Bank,并延長在每一Bank上完成命令所需的時間這一方法能夠改善性能,是由于降低了因tRRD、tFAW和tRC內存時序參數所導致延遲的概率::

tRC:內存的行周期時間。這是觸發同一Bank中不同行所需的最小時間。

tRRD:行-行延遲。這是觸發不同Bank中不同行所需的最小時間。

tFAW:4激活窗口。該時序參數的含義是,在一個tFAW窗口內,不能發出4個以上的激活(active)命令。LPDDR4標準將其設為tRRD的4倍,因此,對于LPDDR4,它們實際上是相同的定時約束,對于其他內存,可能會采用tRRD和tFAW之間的不同關系。

評論