信號完整性(一):PCB走線中途容性負載反射

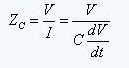

首先按看一下對信號發射端的影響。當一個快速上升的階躍信號到達電容時,電容快速充電,充電電流和信號電壓上升快慢有關,充電電流公式為:I=C*dV/dt。電容量越大,充電電流越大,信號上升時間越快,dt越小,同樣使充電電流越大。

本文引用地址:http://www.104case.com/article/201808/385468.htm我們知道,信號的反射與信號感受到的阻抗變化有關,因此為了分析,我們看一下,電容引起的阻抗變化。在電容開始充電的初期,阻抗表示為:

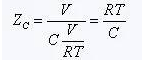

這里dV實際上是階躍信號電壓變化,dt為信號上升時間,電容阻抗公式變為:

從這個公式中,我們可以得到一個很重要的信息,當階躍信號施加到電容兩端的初期,電容的阻抗與信號上升時間和本身的電容量有關。

通常在電容充電初期,阻抗很小,小于走線的特性阻抗。信號在電容處發生負反射,這個負電壓信號和原信號疊加,使得發射端的信號產生下沖,引起發射端信號的非單調性。

對于接收端,信號到達接收端后,發生正反射,反射回來的信號到達電容位置,那個樣發生負反射,反射回接收端的負反射電壓同樣使接收端信號產生下沖。

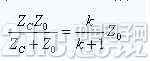

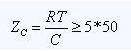

為了使反射噪聲小于電壓擺幅的5%(這種情況對信號影響可以容忍),阻抗變化必須小于10%。那么電容阻抗應該控制在多少?電容的阻抗表現為一個并聯阻抗,我們可以用并聯阻抗公式和反射系數公式來確定它的范圍。對于這種并聯阻抗,我們希望電容阻抗越大越好。假設電容阻抗是PCB走線特性阻抗的k倍,根據并聯阻抗公式得到電容處信號感受到的阻抗為:

阻抗變化率為:

,即

,也就是說,根據這種理想的計算,電容的阻抗至少要是PCB特性阻抗的9倍以上。實際上,隨著電容的充電,電容的阻抗不斷增加,并不是一直保持最低阻抗,另外,每一個器件還會有寄生電感,使阻抗增加。因此這個9倍限制可以放寬。在下邊的討論中假設這個限制是5倍。

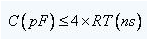

有了阻抗的指標,我們就可以確定能容忍多大的電容量。電路板上50歐姆特性阻抗很常見,我就用50歐姆來計算。

得出:

即在這種情況下,如果信號上升時間為1ns,那么電容量要小于4皮法。反之,如果電容量為4皮法,則信號上升時間最快為1ns,如果信號上升時間為0.5ns,這個4皮法的電容就會產生問題。

這里的計算只不過是為了說明電容的影響,實際電路中情況十分復雜,需要考慮的因素更多,因此這里計算是否精確沒有實際意義。關鍵是要通過這種計算理解電容是如何影響信號的。我們對電路板上每一個因素的影響都有一個感性認識后,就能為設計提供必要的指導,出現問題就知道如何去分析。精確的評估需要用軟件來仿真。

總結:

1、PCB走線中途容性負載使發射端信號產生下沖,接收端信號也會產生下沖。

2、能容忍的電容量和信號上升時間有關,信號上升時間越快,能容忍的電容量越小。

評論