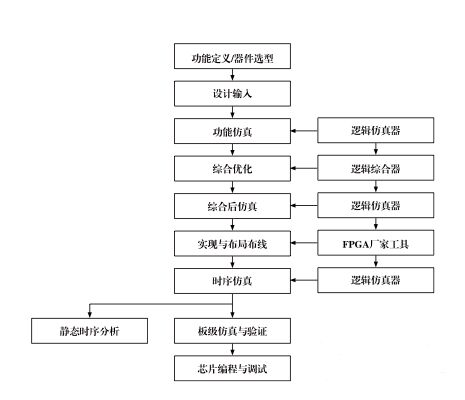

FPGA開發基本流程有哪些?

5、 綜合后仿真

綜合后仿真檢查綜合結果是否和原設計一致。在仿真時,把綜合生成的標準延時文件反標注到綜合仿真模型中去,可估計門延時帶來的影響。但這一步驟不能估計線延時,因此和布線后的實際情況還有一定的差距,并不十分準確。目前的綜合工具較為成熟,對于一般的設計可以省略這一步,但如果在布局布線后發現電路結構和設計意圖不符,則需要回溯到綜合后仿真來確認問題之所在。在功能仿真中介紹的軟件工具一般都支持綜合后仿真。

圖4-1 FPGA典型設計流程

6、 實現與布局布線

布局布線可理解為利用實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能鏈接的布線通道進行連線,并產生相應文件(如配置文件與相關報告),實現是將綜合生成的邏輯網表配置到具體的FPGA芯片上,布局布線是其中最重要的過程。布局將邏輯網表中的硬件原語和底層單元合理地配置到芯片內部的固有硬件結構上,并且往往需要在速度最優和面積最優之間作出選擇。布線根據布局的拓撲結構,利用芯片內部的各種連線資源,合理正確地連接各個元件。目前,FPGA的結構非常復雜,特別是在有時序約束條件時,需要利用時序驅動的引擎進行布局布線。布線結束后,軟件工具會自動生成報告,提供有關設計中各部分資源的使用情況。由于只有FPGA芯片生產商對芯片結構最為了解,所以布局布線必須選擇芯片開發商提供的工具。

7、 時序仿真

時序仿真,也稱為后仿真,是指將布局布線的延時信息反標注到設計網表中來檢測有無時序違規(即不滿足時序約束條件或器件固有的時序規則,如建立時間、保持時間等)現象。時序仿真包含的延遲信息最全,也最精確,能較好地反映芯片的實際工作情況。由于不同芯片的內部延時不一樣,不同的布局布線方案也給延時帶來不同的影響。因此在布局布線后,通過對系統和各個模塊進行時序仿真,分析其時序關系,估計系統性能,以及檢查和消除競爭冒險是非常有必要的。在功能仿真中介紹的軟件工具一般都支持綜合后仿真。

8、 板級仿真與驗證

板級仿真主要應用于高速電路設計中,對高速系統的信號完整性、電磁干擾等特征進行分析,一般都以第三方工具進行仿真和驗證。

9、 芯片編程與調試

設計的最后一步就是芯片編程與調試。芯片編程是指產生使用的數據文件(位數據流文件,Bitstream GeneraTIon),然后將編程數據下載到FPGA芯片中。其中,芯片編程需要滿足一定的條件,如編程電壓、編程時序和編程算法等方面。邏輯分析儀(Logic Analyzer,LA)是FPGA設計的主要調試工具,但需要引出大量的測試管腳,且LA價格昂貴。目前,主流的FPGA芯片生產商都提供了內嵌的在線邏輯分析儀(如Xilinx ISE中的ChipScope、Altera QuartusII中的SignalTapII以及SignalProb)來解決上述矛盾,它們只需要占用芯片少量的邏輯資源,具有很高的實用價值。

評論