厚翼科技內存測試解決方案BRAINS于物聯(lián)網之應用

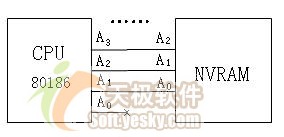

物聯(lián)網相關話題近年來持續(xù)發(fā)燒,引爆巨大的市場商機,根據研調機構Gartner的市場研調報告稱,全球每秒接入物聯(lián)網的設備將達63臺,并預估2015-2020年物聯(lián)網市場規(guī)模將達千億美元量級。物聯(lián)網已經滲透到各行各業(yè)與日常生活中,并極大地擴展監(jiān)控并測量真實世界中發(fā)生的事情的能力。物聯(lián)網將物品和因特網連接起來,含有物聯(lián)網芯片裝置可進行監(jiān)控與測量進行信息交換和通信,而物聯(lián)網芯片為了提供與儲存更多的數據,在相關芯片設計上,使用到只讀存儲器(Read-Only Memory,ROM)與靜態(tài)隨機存取內存(Static Random-Access Memory,SRAM)的容量也比過往的大。

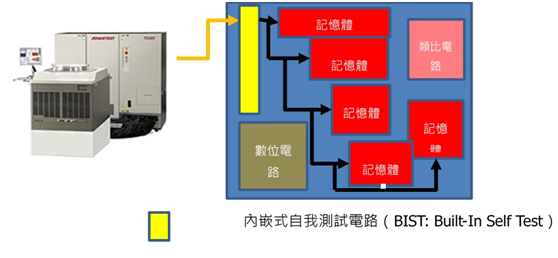

本文引用地址:http://www.104case.com/article/201801/374300.htm為確保芯片上的內存工作正常,內建自我測試技術 (BIST; Built-In Self -Test) 成為芯片實作中,不可或缺的一部分。因此,厚翼科技(HOY technologies)特別開發(fā)「整合性內存自我測試電路產生環(huán)境-BRAINS」,以解決傳統(tǒng)設計之不足。自我測試電路 (Built-In Self-Test)可以提高測試的錯誤涵蓋率,縮短設計周期,增加產品可靠度,進而加快產品的上市速度。傳統(tǒng)的測試做法是針對單一嵌入式內存開發(fā)嵌入式測試電路,所以會導致芯片面積過大與測試時間過久的問題,進而增加芯片設計的測試費用與銷售成本。此外,傳統(tǒng)內存測試方法無法針對一些缺陷類型而彈性選擇內存測試的算法,將導致內存測試結果不準確。

1.整合性內存自我測試電路產生環(huán)境-BRAINS

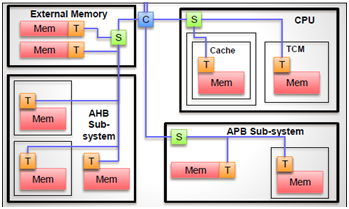

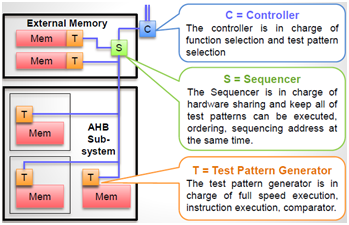

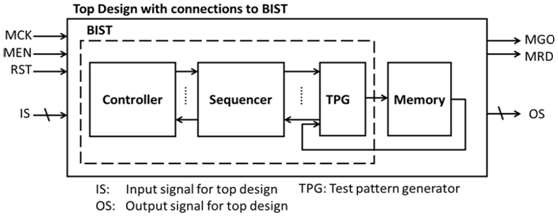

BRAINS是從整體的芯片設計切入,利用硬件架構共享的觀念,創(chuàng)造使用者能輕易產生優(yōu)化的BIST電路工具。

厚翼科技硬件架構共享

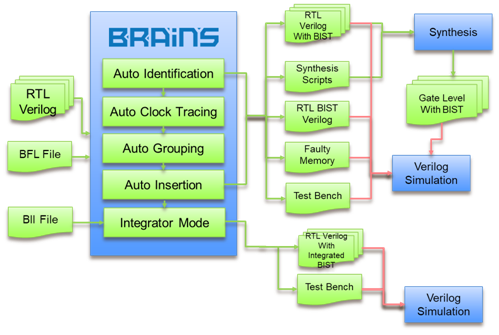

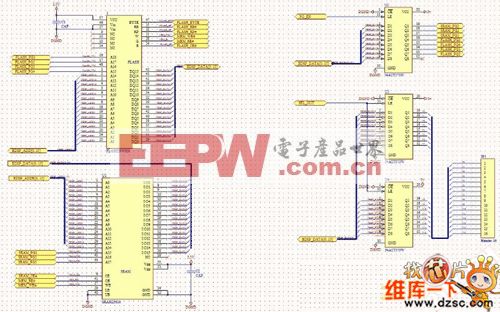

內存測試電路整合性開發(fā)環(huán)境-BRAINS,基本架構圖如下:

BRAINS有下列功能:

n支持RTL和Gate-level格式

n透過BFL (BRAINS Feature List)設定BRAINS的功能

n自動進行內存判別

n自動產生Testbench

n自動嵌入BIST到原設計

n自動追蹤 Clock Source

n透過UDM (User DefinedMemory) 檔案支持用戶自行定義的內存

在機臺與BIST測試操作時,BIST的頻率操作可以為由機臺提供或芯片本身提供:

1.1.BIST的頻率操作由機臺提供時,BRAINS的相關設定為clock_trace= no與clock_switch_of_memory = yes,BRAINS在生成BIST電路,對于內存Clock接到MCK。

未來在機臺與BIST測試時,機臺提供Clock到BIST MCK進行BIST測試。

nclock_switch_of_memory :When this option set to “yes”, the clock signal of memory model will be changedto MCK by clock multiplexer in test mode. The clock frequency of MBIST circuitsand memories are running at same frequency in test mode.

1.2.BIST的頻率操作由芯片提供BRAINS相關的設定如下:

BIST Function設定:

nclock_trace : Please setthis option to “yes”. It is in charge of disabling/ enabling clock tree tracingfunction.

ninsertion : Please set thisoption to “yes”. It is used to integrate generated MBIST circuits and originalsystem designs.

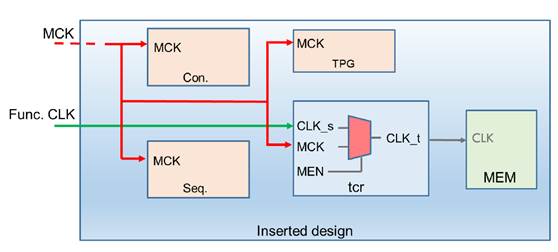

The block diagram forintegrated system design

The block diagram forintegrated system design

nintegrator_mode : Pleaseset this option to “yes”. It is used to add dedicated test port in top modulefor MBIST circuits based on interface option.

Ifthis option is set to “yes”, BRAINS will reserve signals internally for testonly. In this case (set to “yes”), users can use share pin

nauto_group : Please setthis option to “yes”. BRAINS provide auto-grouping function to group memorymodels based on settings in “GROUP” function block automatically.

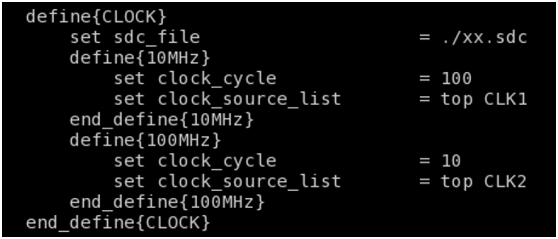

Clock Fuction設定:

nsdc_file : The path of SDCfile.

ndefine{clock_name} : Setclock domain name

nclock_cycle : Set workingperiod (ns) of clock domain defined in “clock_name”.

nclock_source_list: Set source pin or port of clock domain defined in “clock_name”. please divideeach hierarchy by space. If there are more than one source, please divide eachsource by comma.

因應晶圓廠提供的cell library 不同,BRAINS 提供給使用者能將cell library的行為加入到BRAINS 數據中,能避免BRAINS在clocktracing的過程被中斷。

BRAINS 的相關設定將要自定義的cell library的行為加入到BRAINS:

nset user_cell = ./cell_info_name.info

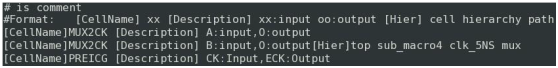

自定義的cell library的格式:

例如,cell library定義其中的MUX2CK(.A( ) , .B( ) , .O( ) , .SEL( )),MUX2CK的行為A 與 B為Inputport ,O為Outpot port,SEL為Select。在cellinfo中定義[CellName] MUX2CK[Description] A:input , O:output,BRAINS clocktracing執(zhí)行時,當碰到MUX2CK時,Clock的來源會判斷為由portA 提供。此外如果在cellinfo中相同的cell name需要有不同的輸入源時,[CellName]MUX2CK [Description] B:input , O:output再加上[Hier] hierarchy定義時,BRAINS clock tracing執(zhí)行時,當碰到hierarchy等于 [Hier]的內容時,當下cell的定義依據定義,選擇不同的輸入來源。

當產生BIST后,因為每一組BIST 控制電路的Clock 來源尚未和芯片上的Clock接通。要如何與芯片的Clock相接,BRAINS提供Integration 流程,方便用戶整合芯片設計與 BIST電路。

1.3.BIST的頻率操作由芯片提供與外部提供并存。

2.總結:

內存測試電路「整合性內存自我測試電路產生環(huán)境-BRAINS」提供多元化的Clock設計,方便使用者依其需求選擇應用,加速開發(fā)的時程與提升產品可靠度。

評論