后CMOS時代 Intel稱有12種設想可降低產品功耗

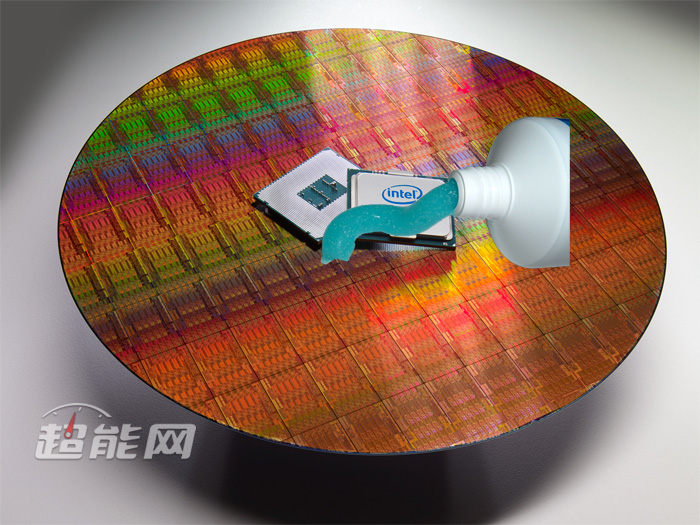

自從14nm節點開始,Intel在傳統CMOS半導體工藝升級上的步伐就慢下來了,Tick-Tock戰略名存實亡,還被TSMC、三星兩家趕超、奚落,甚至連市值都被TSMC超越了,以致于Intel為了挽回面子都想法推動新的半導體工藝命名規則了。傳統CMOS工藝很可能在2024年終結,對此Intel也不是沒有準備,最近他們公布了后CMOS時代的一些技術思路,Intel的目標是在保持現有晶圓工廠的情況下制造功耗更低的產品,電壓可以低至0.5V,這在目前的晶體管下是不可能的。

本文引用地址:http://www.104case.com/article/201704/346282.htm

根據EETimes的報道,在上個月的ISPD 2017(國際物理設計研討會)上,Intel技術制造部門的高級研究員Ian Young介紹了Intel對未來半導體工藝的一些探索,他們的終極目標是希望在使用當前工廠的情況下降低計算過程每一步的功耗。

說得簡單點就是Intel未來會進一步降低計算中的功耗,而且是涉及到每個計算過程,但所有的前提就是兼容現在的半導體工廠——考慮到Intel每代工藝投資都是數十億甚至上百億美元,兼容現在的工廠也是非常正常的需求,這不僅是Intel的希望,整個半導體行業也沒誰愿意放棄現有設備從零開始使用全新的生產技術。

根據Ian Young所說,Intel希望將電源電壓降至遠低于0.5V的水平,但是傳統的CMOS工藝下MOSFET每10年才能降低60mW是不可能實現這個目標的。此外,無論使用什么技術,都需要跟現有的CMOS共存,因為部分時鐘頻率、I/O模擬電路還是需要CMOS晶體管的。

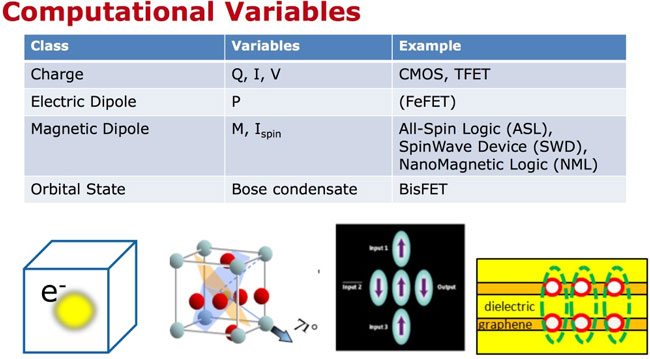

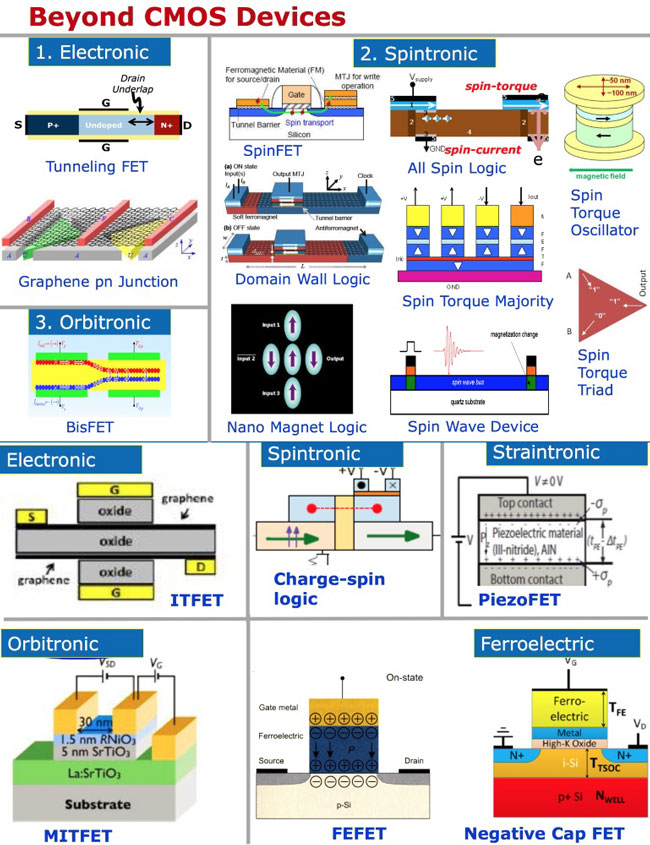

對于后CMOS時代的技術路線,Ian Young稱Intel至少有12種設想可以實現明顯降低電壓的情況下兼容現有半導體工廠,包括電子自旋、磁自旋、Orbitronic、鐵電(Ferroelectric)等等新技術新材料。根據Inel所說,他們已經測試了后CMOS時代邏輯電路各個操作的延遲及能量,了解了他們是如何運行的,建立了行為模型,理解了是如何實現比CMOS低得多的電壓等等問題。

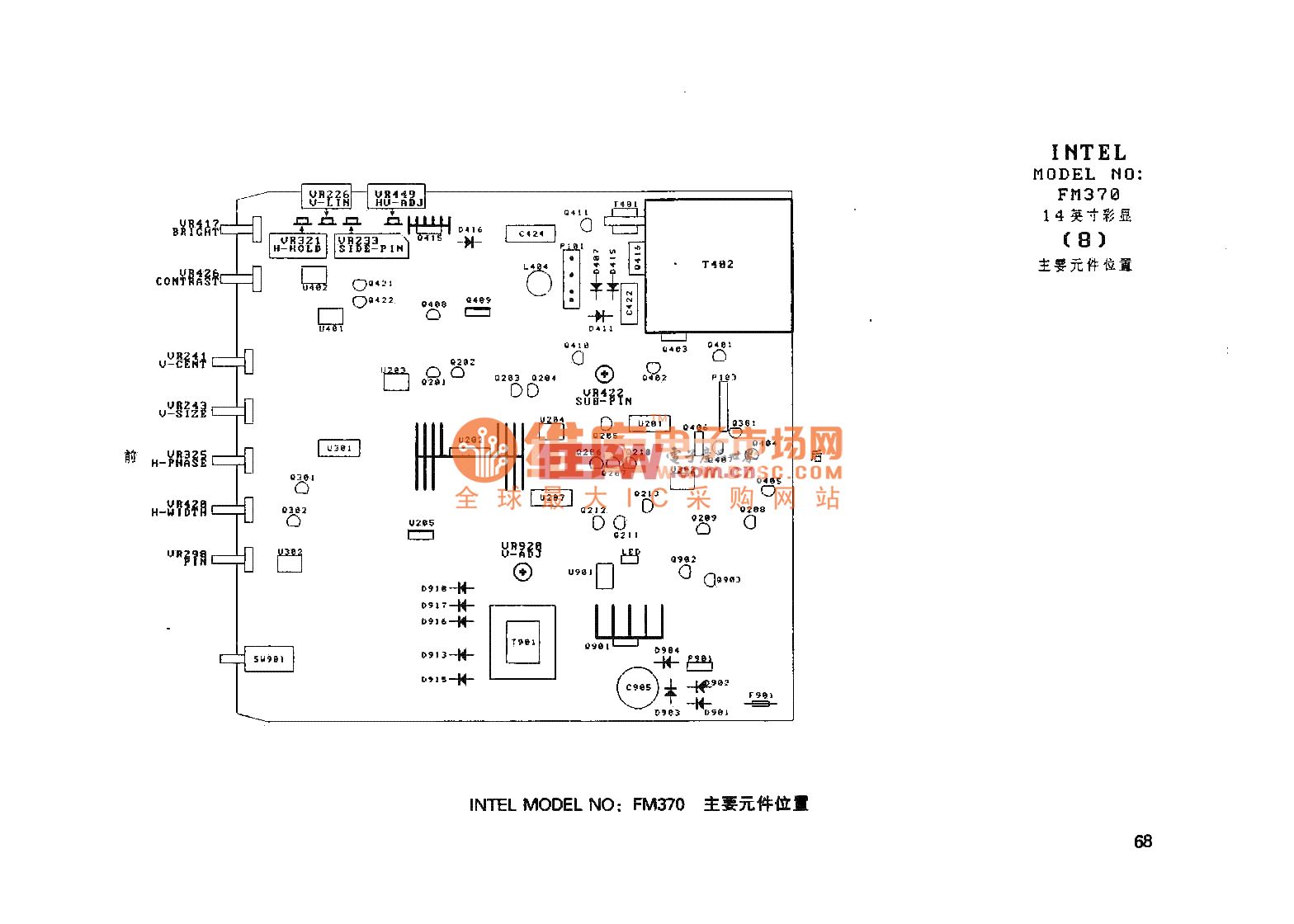

在應對未來的集成電路發展上,應該沒人質疑Intel是有強大的技術實力的(還有一個是IBM),不過話說回來,CMOS時代終結還有較長時間,Intel現在提到的10多種黑科技其實離工業化量產還有段距離,很多技術還是探索階段,下圖中讓普通人的物理老師都頭大的科技依然要等很久才能真正發揮作用。

評論