一文通解基于VLT技術的新型DRAM內存單元

VLT內存單元

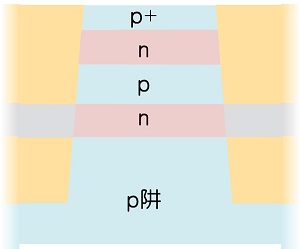

本文引用地址:http://www.104case.com/article/201701/342389.htmKilopasss的全新內存單元基于一種垂直分布的閘流體(也被稱為半導體控制整流器,或SCR)。這種采取pnpn結構的堆棧建構于一個p-阱上,可帶走來自底部n型層的任何空洞。

圖6:VLT內存單元:帶有寫入輔助的PMOS晶體管的閘流體

在淺溝槽隔離(STI)結構中植入一個埋入式字符線,使底部的n層連接到一個字符。埋入式字符線與外部銅金屬M1層字符線透過具有較大電阻的金屬鎢實現連接,因而可以制造比傳統DRAM更長的字符線。

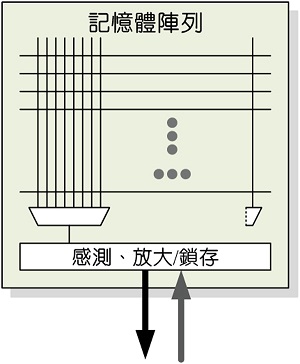

由于感測機制并非采用電荷分配,使感測放大器可承受更長的位線。因此,這種技術可以支持高達2Kbit寬、4Kbit深或總共8M位的MAT——遠大于傳統的DRAM MAT。采用更少片較大型MAT拼接成的內存芯片較采用多片小尺寸MAT的花費更低,因而可使VLT內存的數組效率達到77%,相形之下,同樣采用2x-nm節點的傳統DRAM效率只有64%。

以VLT內存單元打造LPDDR4內存

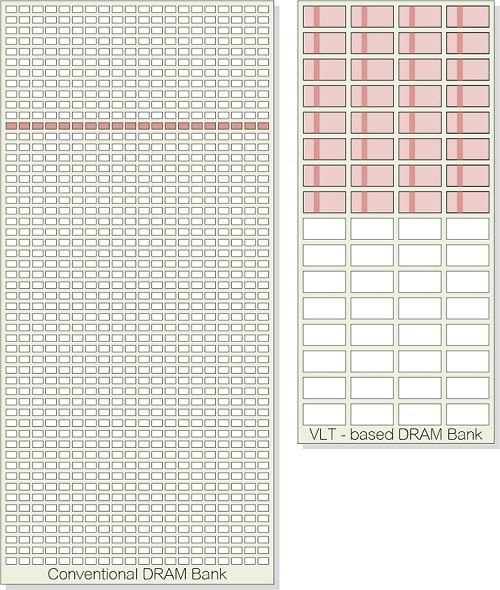

MAT容量增大后,LPDDR4內存組就可以用更少的MAT組成。單純按照位數計算,基于VLT技術的內存組將包含64個MAT,相形之下,傳統DRAM的內存組需要配置848個更小的MAT。不過,接下來的問題就是如何最有效配置這些MAT。

一種配置方式是每個MAT都帶有512個支持4K位線的感測放大器,這意味著每個感測放大器都有多任務器用于在8條位線中進行選擇。其中,多任務器的選擇基于CAS地址;進一步針對圖3的內存數組進行修改后,新的原理圖如下:

圖7:為VLT內存添加位線多任務器

因此,對于每個被選定的分頁,每個MAT中只有八分之一的位線會被選擇,這與普通DRAM實現方式中所有位線都被選中的情況不同。但在傳統DRAM中并不可能實現這種更高效率的感測放大器使用方式,因為所有的位線都必須被讀取,以實現回寫的目的。由于VLT讀取并不是破壞性的,因而無需回寫操作,且多個內存單元可共享感測放大器。

另一個問題是如何在一個MAT實體數組中配置這些MAT。基于VLT MAT的靈活性,實體上配置這些MAT可以不必與邏輯上的配置完全吻合。只要妥善安排各總線的路徑,任何形式的配置都是可能的。舉例來說,一個內存組可被配置為4×16個MAT數組,同時傳輸理論上與傳統LPDDR4相同的數據。

圖8說明傳統DRAM和VLT技術在內存分頁選擇上有什么不同:傳統DRAM選擇一行中的所有MAT,而VLT則從中選擇了一個4×8的MAT區塊。

圖8:內存分頁選擇,其中被選定的MAT是紅色的。傳統DRAM透過行來選擇分頁,而VLT DRAM則以單元區塊選擇分頁。

由VLT制造的LPDDR4,在外部操作上與傳統LPDDR4完全相同。內部操作可能有所差異,例如不必再回寫和預充電,但這并不會影響DDR控制器;如果滿足了VLT的時序要求,其內存的邏輯組織方式與傳統DDR完全一致。

免除刷新

VLT內存單元最明顯的優點之一就是不需要刷新。不過,刷新已經成為DRAM作業的一部份了;無論內存處于閑置狀態或是被接通,都必須進行刷新操作,以避免數據丟失。

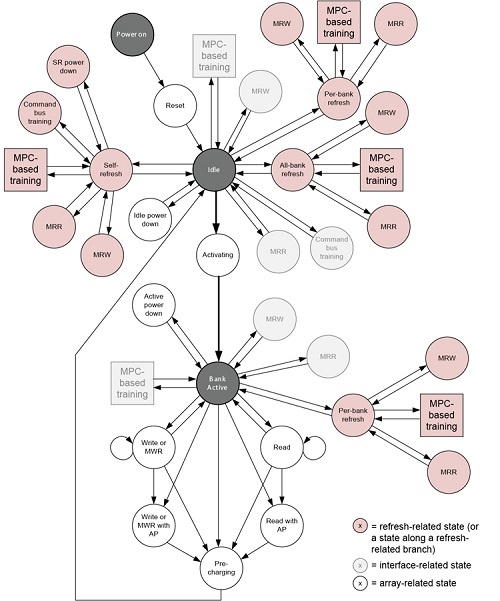

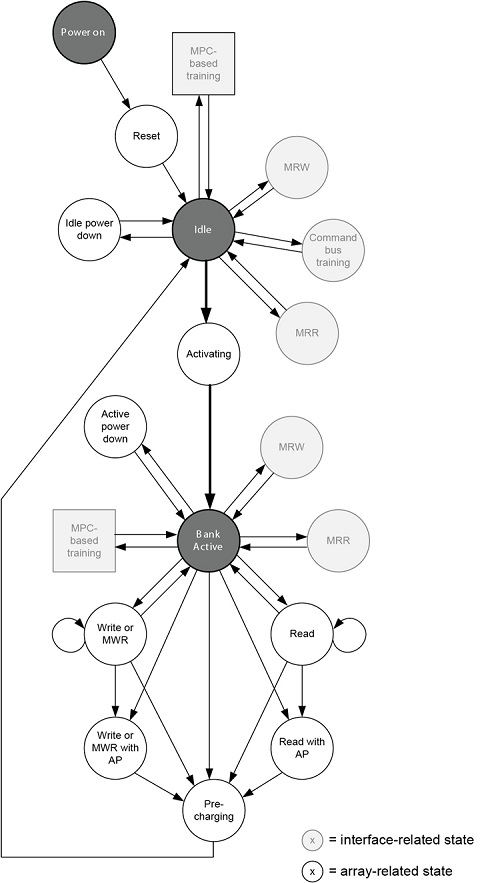

完整的DDR控制器狀態機說明了刷新對于運作的影響,如圖9所示,所有紅色的狀態都與刷新或者基于刷新的分支相關;而使用了VLT技術,這些狀態都是冗余的,而且能夠被消除。

圖9:傳統DRAM建置的LPDDR4狀態原理圖,與刷新有關的狀態以及與基于刷新的有關分支狀態都被標注為紅色,標注為灰色的狀態則與接口相關。

圖10則是一種簡化的狀態機,其中與刷新有關的狀態都已經移除了。在設計基于VLT的內存時,設計者可以選擇現有的DDR控制器,因應那些不需要的狀態加以調整;也可以設計優化的DDR控制器,省去所有與刷新相關的電路——這種方法將占用更小的芯片面積,以及降低功耗。無論選擇哪一種控制器,都不會影響其他系統與內存芯片的互動。

圖10:移除與刷新相關狀態后的LPDDR4狀態原理圖

結語

VLT內存單元可以打造一種比普通DRAM內存單元成本更少、功耗更低的內存,目前VLT內存芯片已能與現有的LPDDR4內存完全兼容了。透過適當設計架構、命令以及時序,VLT內存芯片就能與傳統內存芯片無差別地應用在實際系統上。

基于VLT的內存數組采用一個可在內部作業處理差異的接口,使其得以與標準的LPDDR4控制器配合使用。換句話說,設計一款免刷新的LPDDR4控制器,使其仍具備完整的控制器功能以支持外部接口,并確保現有驅動器都能繼續正常作業,而只是在內部忽略與刷新有關的操作,將有助于大幅節省成本,以及降低功耗。

評論