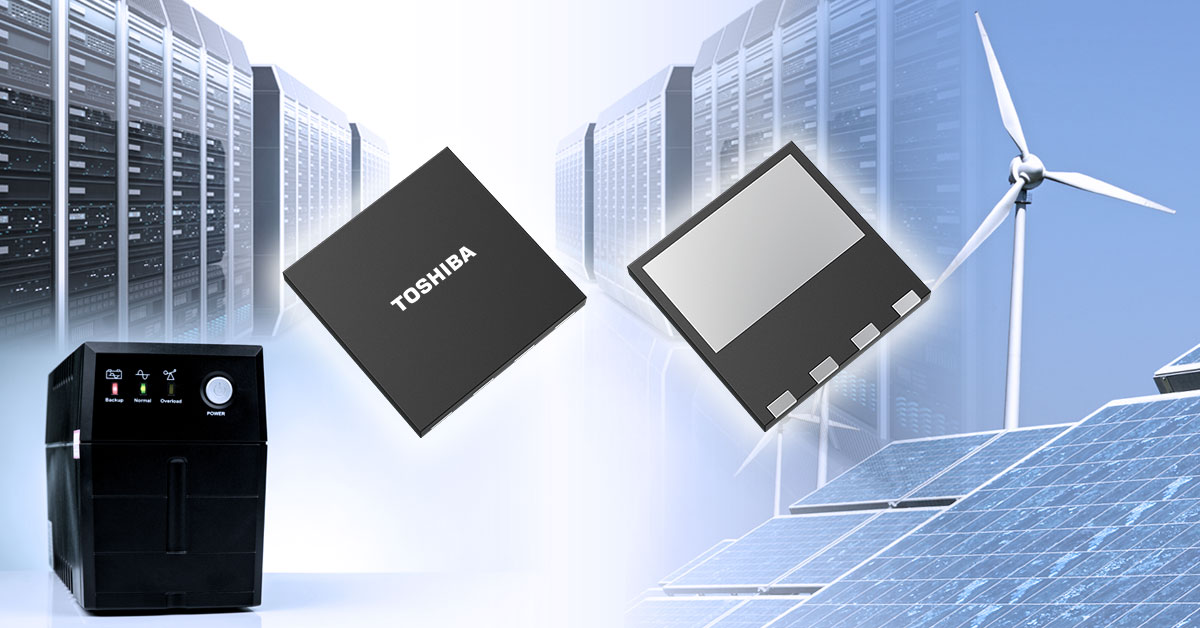

東芝副社長:“3D NAND將挑戰200層單元積層”

“三維閃存需要挑戰200層左右的存儲單元積層”。東芝代表執行董事副社長兼存儲與電子元器件解決方案公司社長成毛康雄在2016年12月14日開幕的半導體相關展會“SEMICON Japan 2016”(東京有明國際會展中心)的“半導體高端論壇”上登臺發言,并如此介紹了該公司的三維閃存(3D NAND)高密度化戰略。

本文引用地址:http://www.104case.com/article/201612/341691.htm成毛以對比15nm工藝2D NAND(二維閃存)的形式,介紹了東芝供應的3D NAND“BiCS FLASH”(48層TLC產品)。BiCS與現有2D NAND相比,存儲元件密度可達到兩倍以上,可靠性(擦寫次數)可提升至約10倍,性能(程序速度)可提高至約兩倍,功耗可降至約一半。存儲芯片的最大容量方面,15nm工藝2D NAND僅為128Gbit,而48層3D NAND可達到256Gbit。東芝打算運用3D NAND的這些優點,開拓數據中心用SSD等要求容量大、可靠性高的市場和用途。

而且,東芝已從2016年7月開始提供64層3D NAND(256Gbit產品)樣品,并投放了量產晶圓。成毛稱,“2017年可通過64層產品覆蓋相當一部分供應bit”,對啟動量產充滿信心。據稱,該公司目前正在開發512Gbit的3D NAND。

成毛就3D NAND表示,東芝今后將為進一步實現高集成化和低成本化開發多種技術。關于三維方向存儲單元積層,成毛稱,“當然會推進100層的單元積層”,然后表示,該公司的目標是實現篇首提到的200層。而且,隨著積層數量的増加,東芝還將致力于縱向尺寸的縮小(薄型化)。另外,關于縮小芯片面積的技術,該公司將推進外圍電路和存儲陣列的高效配置。成毛表示,“將把外圍電路配置在存儲單元下面”。

評論