盤點用了三星14nm FinFET 制程的產品

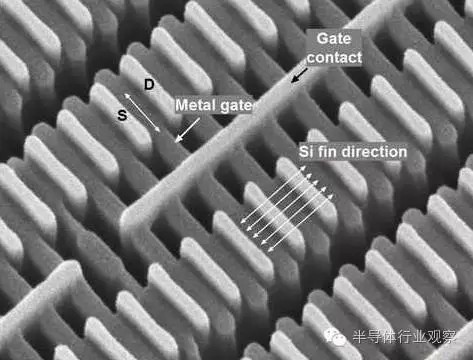

我們從觀察典型三星14 nm LPE FinFET晶體管的SEM側視圖開始(圖1)。晶體管通道如同矽鰭片(Si Fin)般地形成,而非由圖片的左下角向右上方生長。這些鰭片被埋在電介質下方而無法直接看到,因此,我們以箭號指示其方向。金屬閘就位于正交方向,覆蓋在整個鰭片的兩側與頂部。在閘電極的任一側可看到較大的源極與汲極(S/D)觸點。

圖1:三星14 nm LPE FinFET晶體管的側視SEM圖

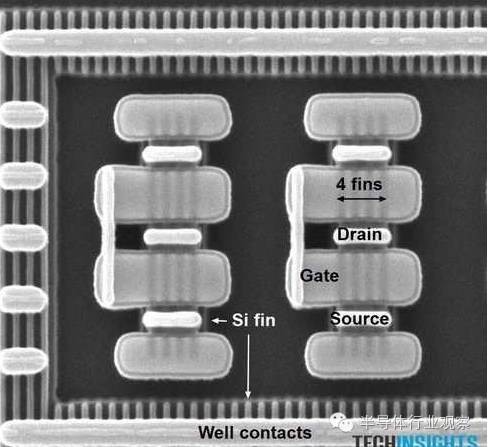

也許從另一張三星FinFET晶體管的平面圖(圖2)中能更清楚的看到閘極與鰭片的布局。四片矽鰭以垂直的方向排列在水平方向的金屬閘極正下方。這兩種晶體管結構周圍都圍繞著一個阱觸環,用于隔離其與芯片上的其他電路部份。

該鰭片間距約有49nm,必須采用雙重圖案制程來制造。在此提供了兩種選擇:英特爾所使用的『雙微影蝕刻』(LELE),或是『自對準雙微影圖案法』(SADP)。我們認為三星采用了LELE制程為鰭片制圖,但最后還需要額外使用光罩與微影制程,才能中斷晶體管的兩端。

圖2:三星14nm FinFET晶體管的平面圖

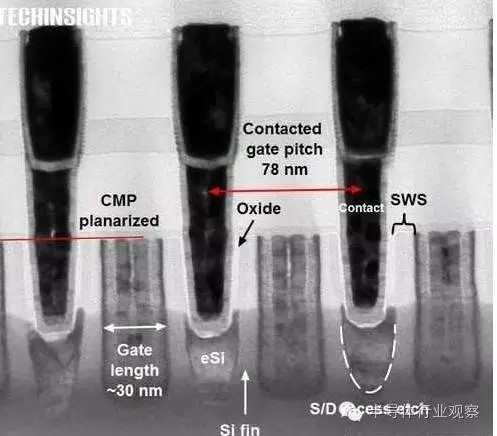

圖3是Exynos 7420所使用的典型NMOS晶體管之TEM橫截面圖,而且我們還注意到閘極長度經測量約有30nm,這跟所宣稱的14 nm制程節點差距頗多,而在表1中所整理的英特爾和臺積電的情況也是一樣的。稍后我們將進一步討論這個問題。

晶體管閘極使用替代性閘極制程制造,包括沉積犧牲層(通常為多晶矽)、圖案化與蝕刻,形成大約30個較寬的條形(stripe)區域。這些條形區域可定義出晶體管閘極長度。

圖3:三星Exynos 7420的NMOS晶體管橫截面圖

接著,側壁間隔層(SWS)沿著閘極側面形成,并且用于作為掘入蝕刻定義及隨后的外延生長——為NMOS晶體管(eSi)生長矽,以及為PMOS晶體管生長矽鍺(eSiGe )等。在完全形成源極/汲極后,以氧化物填充腔室,接著再進行化學機械研磨(CMP)制程。

PMOS源極/汲極區域的SiGe具有圍繞矽鰭的較大晶格常數,因而在PMOS晶體管上產生壓縮應變,從而提高其驅動電流。大量摻雜的SiGe與NMOS eSi源極/汲極也包覆在鰭片兩側,為鎢填充的觸點提供較大的接觸貼片,從而為晶體管實現更低的接觸電阻。

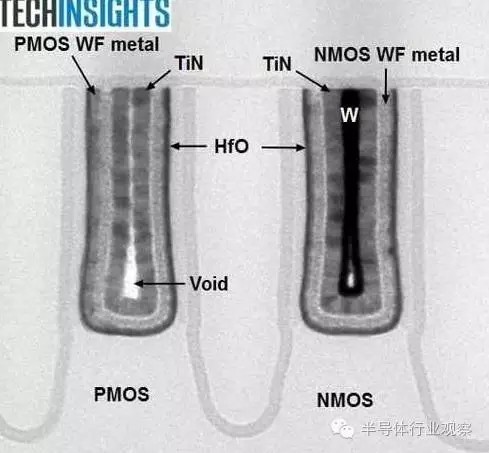

圖4:三星14nm節點的PMOS電晶體管

在此移除該犧牲層閘極,并以其閘電介質與金屬填充該閘極。圖5顯示金屬填充的NMOS與PMOS晶體管,兩個閘極就位于隔離區域的正上方。這些晶體管共用一個通用的氧化鉿(HfO)/氧化物高k閘極電介層堆疊。高密度的HfO隨晶體管邊緣外圍繞的暗帶襯托而清楚顯現。閘極氧化層則環襯在HfO的表面之外。

HfO的內面則環襯著NMOS與PMOS功函數金屬層,用于設定晶體管的閾值電壓,這些金屬分別擁有不同的組成。

閘極填充部份也有一點不同。從圖中可看到NMOS晶體管的內層部份襯著氧化鈦(TiN),再以鎢(W)填充,但PMOS晶體管則不然。閘極長度較短的PMOS晶體管并未使用鎢填充,原因在于TiN封閉閘極頂部,無法再為其填充鎢;而這也導致靠近底部的部份形成真空。在閘極長度較長的PMOS晶體管由于TiN未封閉閘極頂部,因而會再度出現鎢填充。

圖5:虛擬NMOS和PMOS晶體管

我們在前面曾經提到三星的FinFET晶體管較所描述的制程節點長度更長,但并不是只有三星如此。包括英特爾與臺積電所支援的FinFET閘極長度也比其制程節點更長(如表1)。事實上,以微影尺寸的方式來看,與其所宣稱的制程節點也不盡相同。這究竟是怎么一回事?

評論