用Vivado IPI和賽靈思IP實現更快速的設計輸入

本文將介紹如何優化賽靈思內核以便在CPRI遠程無線電頭端設計中使用Vivado IPI。

本文引用地址:http://www.104case.com/article/201610/308385.htm新型基于FPGA的設計使用IP核的數量和種類日趨繁多。Vivado®設計套件中的IP集成器 (IPI) 工具和賽靈思通信IP讓設計人員能夠更加輕松快速地將IP模塊連接在一起。

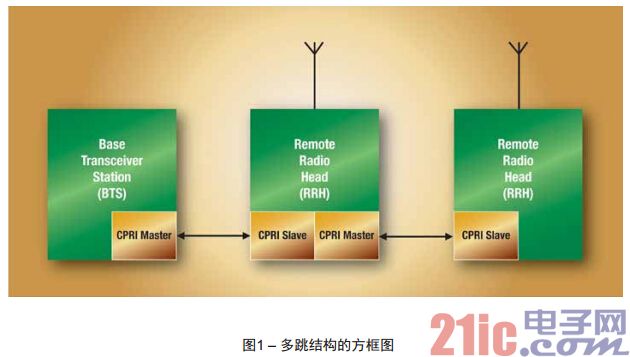

為了更好地闡明IPI方法的強大之處,我們以遠程無線電頭端 (RRH) 為例。RRH位于天線附近,構成蜂窩通信網絡的一部分。它們通常通過光纖連接至上游的基帶收發器站,并可以選擇性地連接到下游的更多RRH,從而構成多跳拓撲結構(圖1)。

通用公共無線電接口 (CPRI) 協議普遍用來連接這些RRH。現在讓我們來構建包含一個上行鏈路CPRI端口和三個下行鏈路CPRI端口且這些端口連接在一起的實例設計。我們可以利用IPI構建出整個設計中的主體部分。然后我們選用Kintex®-7器件,因為該器件具備低功耗、低成本和高性能等優異特性,因此非常適合此實例設計。速度等級為-2的All Programmable 器件Kintex FPGA和Zynq®-7000 SoC中的GTX 收發器支持使用9.8Gbps CPRI線路速率。

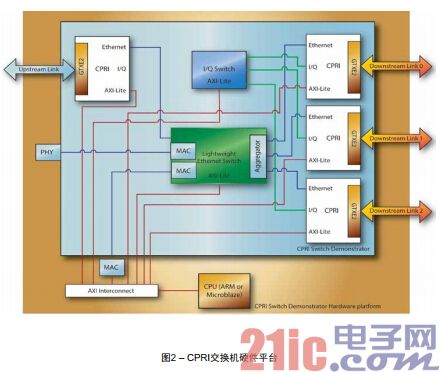

圖2展示了我們在IPI中將要創建的內容。我們可建立模塊設計,并從IP Catalog中實例化所需的IP。標準賽靈思IP Catalog中提供有CPRI內核。該內核經過優化,不僅可實現資源共享(可能情況下),而且還能簡化在IPI中的使用。交換機屬于自定義IP。

IP核資源共享

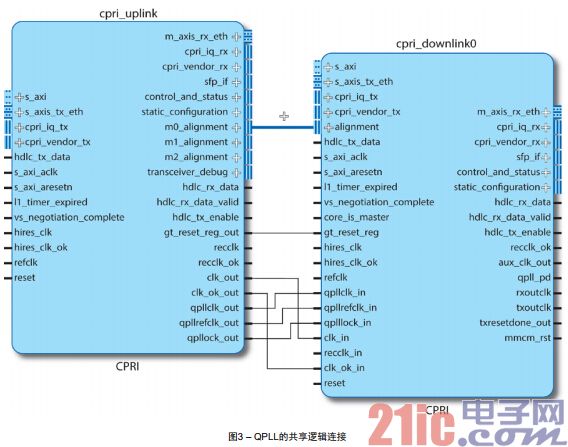

使用多個IP實例時客戶遇到的挑戰之一是如何高效共享資源。很多通信IP核都支持“共享邏輯”功能。對于CPRI內核,我們可用內核中的可共享邏輯資源配置IP,或者省略這些共享資源。如果共享資源包含在內核之中,它們會提供必要的輸出以便讓我們將共享資源連接到不含這些邏輯的內核。

有特殊要求的用戶可能希望在內核中移除這些共享邏輯并實現自己的邏輯。在我們的實例設計中,我們將CPRI內核的運行速度配置為9.8Gbps。這該線路速率下,有必要使用LCtank振蕩器來提供收發器時鐘。Kintex-7器件中的收發器采用Quad布局,每個收發器Quad包含四個收發器通道和一個基于LC-tank的Quad鎖相環 (QPLL)。所有內核都有必要共享QPLL以及由上行鏈路時鐘信號生成的時鐘。圖3中給出了帶有定制共享邏輯的上行鏈路內核上QPLL和時鐘輸出端口,該上行鏈路內核的共享邏輯連接到將不含共享邏輯的下行鏈路CPRI內核的相應輸入端口。

CPRI內核間的數據路由

我們還進行了IQ交換機和以太網交換機的實例化,以便讓數據在內核之間實現路由。

CPRI網絡中的控制和管理數據通過以太網子通道發送。憑借系統中的以太網交換機,可以遠程發布固件升級或命令,并將其發送至任意節點。IP旨在使用盡量少的邏輯資源,因為這種情況沒必要使用功能齊全的以太網交換機。

IQ交換機能以確定的時延在CPRI內核之間路由任何IQ樣本。多跳無線電系統的一個重要特性是可以準確測量鏈路延遲,而且CPRI標準定義了一種能夠協助該測量的方法。

用IPI連接接口

IPI總線接口將定義好的一組邏輯端口映射到IP上的特定物理端口。如果我們盡可能地使用接口,就可以從連接很多信號轉變為連接少量接口。IP上的通用總線接口是符合ARM® AXI標準(例如AXI4-Lite和AXI4-Stream)的接口。這種抽象程度的提高使設計輸入更簡單、更快速,而且使您能夠充分利用接口的設計規則檢查功能。Vivado IP Packager允許您在IPI中使用自己的IP,并在自己的設計中利用這些接口。

IPI便于將接口連接在一起。只需點擊接口,IPI就會指示其可以連接至具體內容。將連接線拖拽到所需的端點,就會建立起來連接。利用該方法,只需點擊幾次就可連接很多信號。

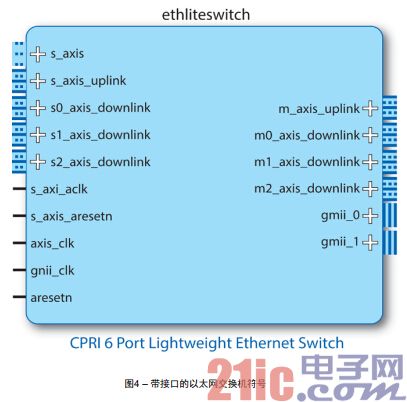

圖4顯示的以太網交換機提供若干AXI4-Stream接口,兩個GMII接口,以及一個AXI4-Lite接口。數據流接口能直接連接到CPRI內核,這樣無需在CPRI內核上進行內部緩沖。GMII接口能連接到以太網PHY,可供工程師在現場調試網絡問題。AXI4-Lite管理接口用來訪問地址表格映射及其它配置選項,例如地址表格老化間隔。

我們繼續以這種方式增強系統,在IPI中連接各個接口。您可以靈活地使用任何最適合的輸入方法。除了使用GUI連接接口外,還可以通過Tcl控制臺直接發命令,或者從腳本獲得命令。每次在GUI中做任何操作時,就會返回相應的命令。

整個設計完成后,使用“write_bd_tcl”命令將整個設計導出。該命令創建一個可引用的Tcl文件,用以從頭創建整個模塊設計,或方便地作為腳本構建流程中的一部分。設計中的所有IP都提供一個AXI4-Lite管理接口,以便讓內核連接到主機處理器。IPI中內置的智能功能可以實現自動化連接。憑借這種機制,IPI就能識別出IP上的AXI4-Lite接口將連接到AXI總線互聯,并自動配置合適的地址范圍,為我們連接到總線。然后,您可借助IPI將該總線連接到主機處理器。本案例中的主機處理器是MicroBlaze™,不過若使用Zynq SoC系列器件,就能方便地將主機處理器改為ARM CPU。

更多優勢接踵而至

Vivado IPI功能正在快速增加,以后還將帶來更多優勢。通過使用正確的IP,我們可以將整個子系統快速集成在一起,并從中受益。

如需了解有關CPRI、以太網交換機或IQ交換機IP方面的更多信息,請發送郵件至:permind@xilinx.com,與賽靈思無線通信部的Perminder Tumber 取得聯系。

評論