FPGA 101:用Vivado HLS為軟件提速

在編寫軟件時,您有沒有遇到過無論怎么努力編碼,軟件都不能按您期望的速度運行?我遇到過。您有沒有想過,“有沒有什么簡單而且成本不高的方法可將一些代碼輸入多個定制處理器或定制硬件?”畢竟,您的應用只是眾多應用中的一個,而且創建定制硬件需要花費時間和成本。是不是這樣?

本文引用地址:http://www.104case.com/article/201610/308462.htm最近聽說了賽靈思的高層次綜合工具Vivado®HLS后,我開始重新思考這一問題。高層次綜合工具與Zynq®-7000 All Programmable SoC的結合為設計開辟了新的可能性,其中Zynq®-7000 All Programmable SoC結合了帶有FPGA架構的雙核ARM®CortexTM-A9處理器。這類工具可以用C語言,C++語言或SystemC源代碼創建高度優化的RTL。近年來,出現很多這項技術的提供商,且其采用率也不斷提高。

如果我只用Vivado HLS便能完成要求更高的計算,那么將那些慢速代碼遷移到硬件中會有多難?畢竟我經常用C++語言編寫代碼,而Vivado HLS將C/C++語言作為輸入語言。ARM處理器內核意味著我可以在常規環境下運行多數軟件。事實上賽靈思還提供了一款軟件開發工具(SDK)以及PetaLinux來幫您實現這一目的。

架構問題

從軟件角度思考這一轉變,我開始更加擔心軟件接口問題。畢竟,HLS創建的硬件專注于處理硬件接口。我需要一些易于訪問的工具(如協處理器或硬件加速器)來加快軟件運行速度。而且,我不想編寫新的編譯器。為了方便與軟件的其它部分交換數據,這個接口應該類似于簡單的存儲單元,我們可以在其中輸入信息并稍后讀取結果。

然后我有了新的發現。Vivado HLS支持以相對較小的努力輕松創建AXI從接口。這讓我開始思考,創建加速器也許沒有那么難。于是,我編碼了一個簡單的實例來探索這種可能性。探索的結果讓我驚喜不已。

下面看看我用了什么方法,并思考這種方法所得出的結果。

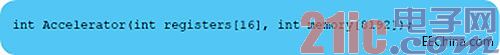

在我的實例中,我選擇了對一系列簡單的矩陣運算(如加法和乘法)進行建模。我不想將它限制在固定的大小,因此,我必須同時提供輸入陣列及各陣列的尺寸大小。理想的接口會將所有數值作為函數的自變量,例如圖1中的代碼。

硬件接口需要用一種簡單的方法將函數自變量映射到存儲單元。圖2是支持這一映射的存儲器配置。寄存器中保存了有關矩陣的排列方式以及所需運算的信息。指令寄存器將指示執行何種運算。這樣我便可以將一些簡單的運算融合到一個硬件中。可以用狀態寄存器來查看是否正在進行運算或是已經成功完成運算。此外,器件最好還能提供中斷支持。

回到硬件設計,我了解到Vivado HLS為陣列自變量留出空間以指定小容量內存。這樣,圖3所示函數便說明了這種函數性。

假設能夠綜合AXI從接口,怎樣將它用在軟件上?我將正常編碼環境假設為Linux。還好賽靈思提供PetaLinux,而且PetaLinux提供一種叫做用戶I/O器件的機制。UIO可以用簡單的方法將新硬件映射到用戶內存空間,并具備中斷等待能力。這意味著您可以省去編寫器件驅動程序所耗費的的時間和流程。圖4顯示了這個系統。

這種方式當然也有缺陷。例如,無法在DMA中使用UIO器件,因此您必須在器件內存中構建矩陣,并在構建完成后手動復制出來。如果需要,將來可以通過定制器件驅動程序解決這個問題。

用Vivado HLS綜合硬件

現在回到綜合AXI從接口的話題。它的綜合難度有多大?我發現這些編碼限制非常合理。除內存的動態分配以外,大多數C ++語言都可以使用。

畢竟硬件在運行過程中不能生產其本身。這限制了標準模板庫(STL)功能的使用,因為這里大量使用了動態分配。只要數據保持靜態,多數功能都可以使用。起初這項任務似乎非常繁重,但我發現這并不是什么大事。另外,Vivado HLS允許C++類、模板、函數和運算符重載。我的矩陣運算可輕易歸入定制矩陣分類。

增加I/O來創建AXI從接口非常簡單。只需增加一些能夠指示包含哪些端口以及使用哪些協議的編譯指示即可。

只要我不按下所有旋鈕,運行這款綜合工具非常簡單。圖5展示了其中各個步驟,在此我不再詳細解釋。需要就目標技術和時鐘速度對Vivado HLS進行一些引導。之后涉及的程序會密切關注違反政策的報告并研究分析報告以確保Vivado HLS按我所期望的方式運行。工具用戶必須對硬件方面有所了解,但有一些技術課程可以解決這個問題。還存在綜合前后運行仿真以檢驗預期行為的問題。

Vivado IP Integrator讓AXI從接口連接到Zynq SoC硬件變得輕而易舉,并打消了對信號連接錯誤的顧慮。賽靈思甚至擁有我所使用的ZedBoard開發系統的系統概述,并用IP Integrator導出數據用于軟件開發套件。

清除瓶頸

我對結果非常滿意,我希望能用這款芯片與工具集的組合做更多事情。我并沒有探索所有的可能性。例如,Vivado HLS還支持AXI主接口。AXI會允許加速器從外部存儲器復制矩陣(盡管這樣也可能存在安全問題)。不過我強烈建議所有面臨代碼瓶頸的人都能考慮這個工具集。這里提供足夠的培訓課程、資源和材料以實現快速勻變,其中包括Doulos提供的課程、資源和材料。如需了解更多信息,敬請訪問:www.doulos.com。

圖1 – 調用加速器示例

圖2 – 寄存器匯總表

圖3 – 加速器函數API

評論