Board從入門到精通系列(六)

由于更新了開發(fā)工具,所以本篇博客有必要重復(fù)前面的內(nèi)容,今天首先演示如何利用Vivado開發(fā)純邏輯工程,即只在PL上進(jìn)行開發(fā)。恰好最近在看雷思磊的《步步驚芯——軟核處理器內(nèi)部設(shè)計分析》,于是將一部分實(shí)驗(yàn)搬到了ZED-Board上進(jìn)行驗(yàn)證。對OpenRISC感興趣的童鞋可以關(guān)注Rill的專欄 進(jìn)一步獲得學(xué)習(xí)資源。

本文引用地址:http://www.104case.com/article/201710/365597.htm先簡要介紹下OpenRISC軟件開發(fā),參考了雷思磊書上建立開發(fā)環(huán)境的步驟。

1.下載GNU開發(fā)環(huán)境,可以直接下載配置好的VirtualBox鏡像,鏈接為 ftp://openrisc.opencores.org/virtualbox-image/ ,F(xiàn)TP用戶名和密碼都是openrisc。下載2011-12-15版本。

2.下載安裝VirtualBox。新建虛擬機(jī),配置為Linux, Ubuntu,512MB內(nèi)存(需求并不高),使用現(xiàn)有虛擬硬盤(OpenRISC_Ubuntu_2011-12-15.vdi)

安裝完成即可啟動。GNU工具鏈為or32-elf-...(可以是ar, as, g++, gcc等等)。root密碼:openrisc

VirtualBox中設(shè)置Windows和虛擬機(jī)的共享文件夾。關(guān)閉Ubuntu系統(tǒng),在VirtualBox主界面中選擇“設(shè)置”,在“數(shù)據(jù)空間”中增加Windows共享文件夾E:Share,在Ubuntu中名稱為Share。設(shè)置完成后,啟動Ubuntu系統(tǒng),終端輸入命令sudo mount -t vboxsf Share /mnt/sharefolder

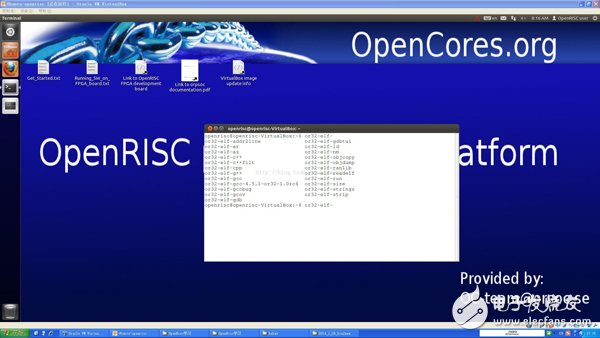

虛擬機(jī)運(yùn)行后如圖(如果圖太大看不完全,可以右鍵另存為圖片后在本地查看)。

3.編寫簡單測試匯編代碼example.s

# Comments like this

# Begin

.secTIon .text, ax

.org 0x100

.global _start

_start:

l.andi r0,r0,0

l.extwz r1,r0

l.extwz r2,r0

l.addi r1,r1,0x0A

l.add r2,r2,r1

l.nop 0x0001

# End

4.

編譯:or32-elf-as example.s -o example.o

鏈接:or32-elf-ld -T ram.ld example.o -o example.or32

鏈接輸入腳本ram.ld內(nèi)容如下:

MEMORY

{

ram : ORIGIN = 0x00000000, LENGTH = 0x00005000

}

SECTIONS

{

.text :

{

*(.text)

} > ram

.data :

{

*(.data)

} > ram

.bss :

{

*(.bss)

} > ram

}

ENTRY (_start)

OR1KSim模擬器運(yùn)行:sim -t example.or32 -m1M > example.trace

生成的跟蹤文件example.trace內(nèi)容如下:

Seeding random generator with value 0x88a2d16e

Or1ksim 2011-08-15

Building automata... done, num uncovered: 0/213.

Parsing operands data... done.

ResetTIng PIC.

loadcode: filename example.or32 startaddr=00000000 virtphy_transl=00000000

Not COFF file format

ELF type: 0x0002

ELF machine: 0x005c

ELF version: 0x00000001

ELF sec = 5

SecTIon: .text, vaddr: 0x00000000, paddr: 0x0 offset: 0x00002000, size: 0x00000118

S 00000100: a4000000 l.andi r0,r0,0 r0 = 00000000 flag: 0

S 00000104: e020004d l.extwz r1,r0 r1 = 00000000 flag: 0

S 00000108: e040004d l.extwz r2,r0 r2 = 00000000 flag: 0

S 0000010c: 9c21000a l.addi r1,r1,0xa r1 = 0000000a flag: 0

S 00000110: e0420800 l.add r2,r2,r1 r2 = 0000000a flag: 0

exit(0)

@reset : cycles 0, insn #0

@exit : cycles 5, insn #6

diff : cycles 5, insn #6

從上述結(jié)果可以看到軟件仿真的結(jié)果,注意r1,r2的值變化情況,后面硬件仿真時會看到。

導(dǎo)出二進(jìn)制文件:or32-elf-objcopy -O binary example.or32 mem.bin

上述步驟、命令行參數(shù)具體含義請參考原書,此處略過不提。

為了將mem.bin文件轉(zhuǎn)換為Vivado Simulator可識別的格式,博主用matlab編寫了格式轉(zhuǎn)換程序bin2mem.m,代碼如下:

clear;

clc;

close all;

fid = fopen(mem.bin,rb);

mem = fread(fid,uint8);

fclose(fid);

mem = reshape(mem,4,[]);

mem = [65536*256,65536,256,1]*mem;

fid = fopen(mem.data,w);

fprintf(fid,%08xrn,mem);

fclose(fid);

得到mem.data后宣告OpenRISC軟件開發(fā)的結(jié)束。下面利用Vivado進(jìn)行硬件平臺開發(fā)。

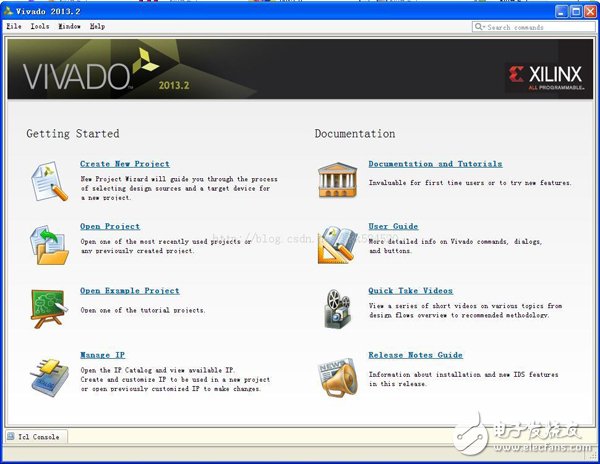

首先獲得Vivado 2013.2軟件,可以從xilinx官網(wǎng)下載。最新版的博主沒有用過,不能保證所有操作步驟都一致,需要讀者自行協(xié)調(diào)。

安裝完成后,運(yùn)行Vivado,雙擊下面圖標(biāo),左側(cè)為IDE,右側(cè)為HLS,本實(shí)驗(yàn)只用IDE。

啟動后歡迎界面如下

選擇Create New Project,如下設(shè)置項(xiàng)目名稱

一直按下一步,到如下畫面后為止

選擇器件,先點(diǎn)Specify中的Boards,再點(diǎn)ZedBoard Zynq Evaluation and Development Kit。下一步,直到完成,進(jìn)入IDE。

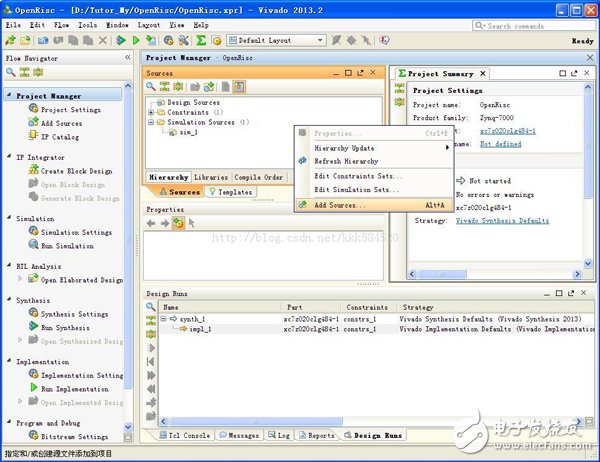

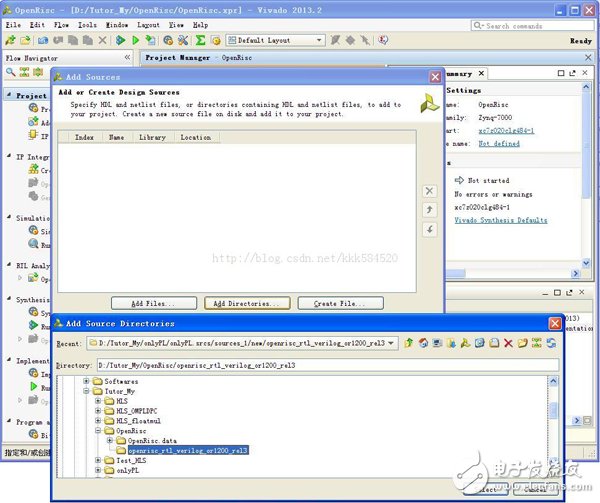

在IDE的Sources窗口中右鍵選擇Add Sources...,添加OpenRisc verilog源碼。我們將openrisc_rtl_verilog_or1200_rel3版本源碼解壓到本地磁盤,還需要將or1200_defines.v, or1200__qmem_top.v, or1200_spram_2048x32.v三個文件進(jìn)行修改,可以下載后直接覆蓋原文件,原書中有詳細(xì)修改說明。

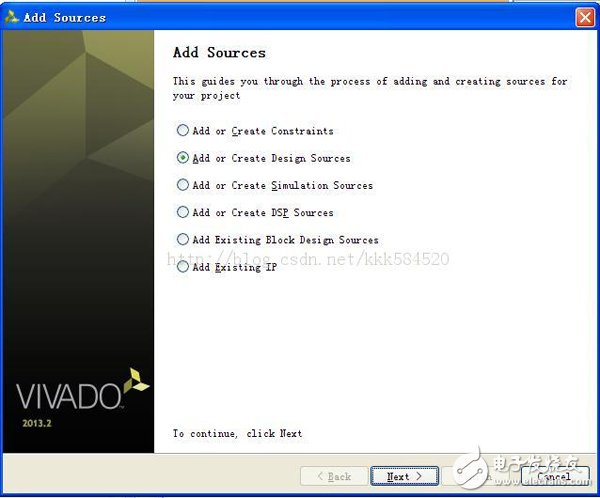

選擇第二項(xiàng),下一步

點(diǎn)Add Directories...選擇源碼存放目錄,確定,返回IDE。這時還需要添加一個仿真激勵文件,我們創(chuàng)建一個文件or1200_tb.v,步驟如下:

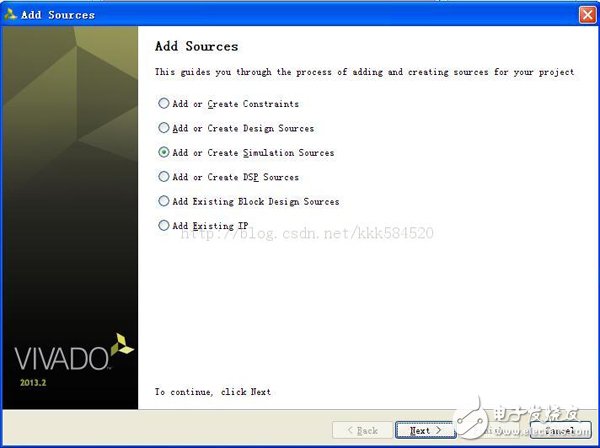

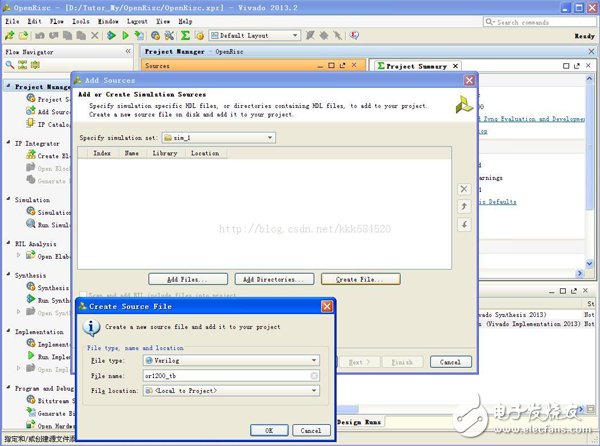

仍然在Sources窗口右鍵,Add Sources...

選擇第三項(xiàng),Next

選擇Create File...,輸入or1200_tb,確定,回到IDE。雙擊打開,修改其內(nèi)容如下:

`timescale 1ns / 100ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2014/01/26 12:57:10

// Design Name:

// Module Name: or1200_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module or1200_tb();

reg CLOCK_50;

reg rst;

initial begin

CLOCK_50 = 1b0;

forever #10 CLOCK_50 = ~ CLOCK_50;

end

initial begin

rst = 1b1;

#200 rst = 1b0;

#1000 $stop;

end

or1200_top or1200_top_inst

(

.clk_i(CLOCK_50),

.rst_i(rst),

.pic_ints_i(20b0),

.clmode_i(2b00),

.iwb_clk_i(clk_i),

.iwb_rst_i(rst),

.iwb_dat_i(32b0),

.iwb_ack_i(1b0),

.iwb_err_i(1b0),

.iwb_rty_i(1b0),

.iwb_cyc_o(),

.iwb_adr_o(),

.iwb_dat_o(),

.iwb_stb_o(),

.iwb_we_o(),

.iwb_sel_o(),

`ifdef OR1200_WB_CAB

.iwb_cab_o(),

`endif

.dwb_clk_i(clk_i),

.dwb_rst_i(rst),

.dwb_dat_i(32b0),

.dwb_ack_i(1b0),

.dwb_err_i(1b0),

.dwb_rty_i(1b0),

.dwb_cyc_o(),

.dwb_adr_o(),

.dwb_dat_o(),

.dwb_stb_o(),

.dwb_we_o(),

.dwb_sel_o(),

`ifdef OR1200_WB_CAB

.dwb_cab_o(),

`endif

.dbg_stall_i(1b0),

.dbg_ewt_i(1b0),

.dbg_lss_o(),

.dbg_is_o(),

.dbg_wp_o(),

.dbg_bp_o(),

.dbg_stb_i(1b0),

.dbg_we_i(1b0),

.dbg_adr_i(0),

.dbg_dat_i(0),

.dbg_dat_o(),

.dbg_ack_o(),

.pm_cpustall_i(0),

.pm_clksd_o(),

.pm_dc_gate_o(),

.pm_ic_gate_o(),

.pm_dmmu_gate_o(),

.pm_immu_gate_o(),

.pm_tt_gate_o(),

.pm_cpu_gate_o(),

.pm_wakeup_o(),

.pm_lvolt_o()

);

endmodule

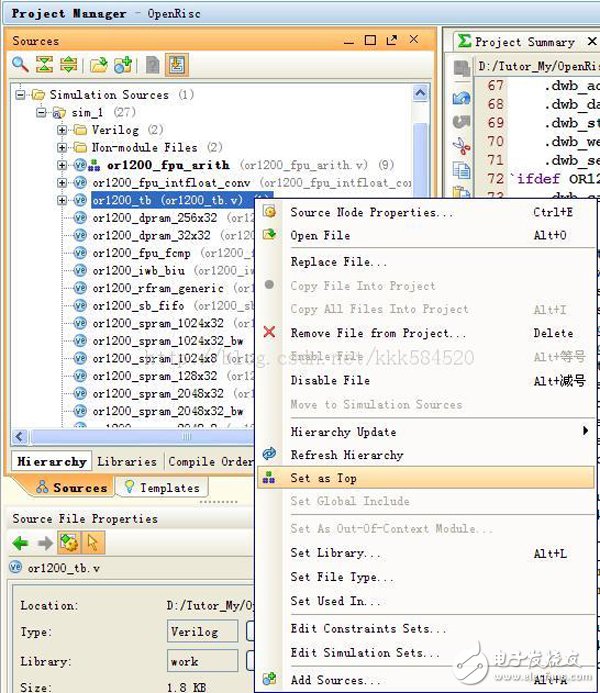

將or1200_tb.v設(shè)為仿真的頂層文件。一切就緒,下面進(jìn)行行為仿真。

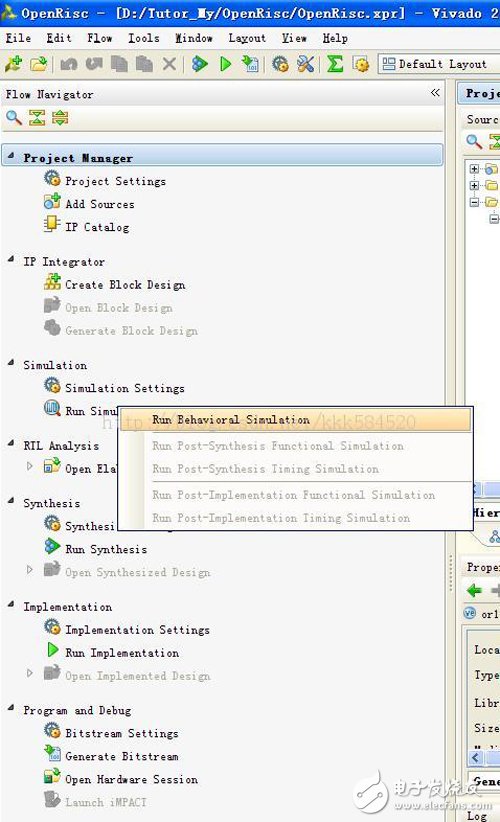

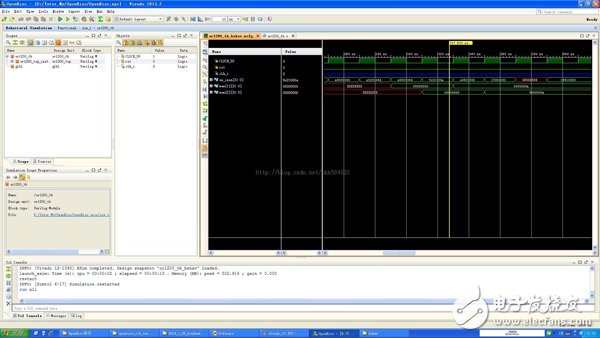

在左側(cè)設(shè)計流程中選擇Run Simulation,接著點(diǎn)行為仿真。經(jīng)過初始化,進(jìn)入Vivado Simulator界面。添加信號or1200_tb/or1200_top_inst/or1200_cpu/or1200_ctrl/ex_insn,or1200_tb/or1200_top_inst/or1200_cpu/or1200_rf/rf_b/mem[1]和mem[2]到波形觀測窗。

將前面生成的OpenRISC代碼mem.data復(fù)制到仿真目錄(根據(jù)你的工程路徑設(shè)置),如下圖

在仿真界面命令行依次輸入restart,run 1000ns后得到結(jié)果如下

對比mem.data文件最后幾行二進(jìn)制代碼:

a4000000

e020004d

e040004d

9c21000a

e0420800

15000001

可以看到,ex_insn信號依次呈現(xiàn)了上述指令,并且能看到mem[1]和mem[2]的值依次變?yōu)?x0000000a。對比前面trace文件可以知道,mem[1]即OpenRISC的r1寄存器,mem[2]即r2寄存器,依次類推。我們在進(jìn)一步學(xué)習(xí)OpenRISC時,可以重點(diǎn)關(guān)注這些寄存器的值變化。

為了直觀看到取指、譯碼、執(zhí)行流水線,我們再加入or1200_tb/or1200_top_inst/or1200_cpu/or1200_ctrl/ex_insn/if_insn和id_insn兩個信號,重啟仿真過程:restart, run all.

可以看到指令沿if,id,ex三個模塊依次流動,實(shí)現(xiàn)了流水線。

本節(jié)工程文件可以到我的資源下載。

結(jié)論:通過Vivado可以替代ISE完成邏輯開發(fā)和驗(yàn)證。

評論