基于FPGA的Alpha半透明圖像疊加算法硬件實現

摘要:文中在FPGA上采用純verilog邏輯實現了Alpha半透明圖像疊加算法,即驗證了算法的正確性,同時針對FPGA不善于處理浮點運算的弊端,采用了移位操作的方法,進一步提高了運算速度,實現了Alpha透明系數可調,半透明圖像疊加的實時顯示,在高清圖像顯示領域具有很大的實用價值。

本文引用地址:http://www.104case.com/article/201609/303572.htmAlpha透明算法被廣泛應用于圖像處理,2D游戲,3D游戲圖像混合和渲染等領域。在涉及到高清圖像時由于計算量比較大,PC處理速度較慢,圖像半透明疊加效果無法實時呈現。本文采用了FPGA并行處理的思想,同時對邏輯中設計到的浮點運算進行了移位操作,極大的提高了運算速度,實現了圖像的半透明疊加效果的實時顯示。可以在高清圖像顯示領域中實現視頻和半透明滾動字幕的疊加,以及多路視頻的實時疊加處理。

1 Alpha算法

Alpha通道是一個8位的灰度通道,該通道用256灰度來記錄圖像中透明度信息、定義透明、不透明和半透明區域,其中黑表示全透明,白表示不透明,灰表示半透明。

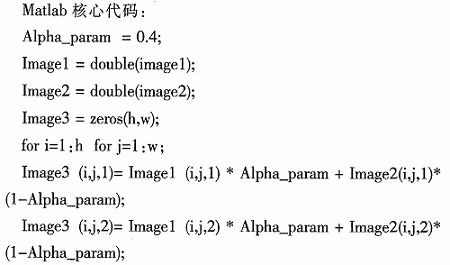

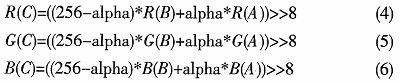

Alpha混合算法公式:

R(A)、G(A)、B(A)分別代表圖像A的RGB分量的原色值,R(B)、G(B)、B(B)分別代表圖像B的RGB分量的原色值,R(C)、G(C)、B(C)分別代表混合后圖像C的RGB分量的原色值。

alpha為圖像的透明度系數,取值為0—1,1為完全透明,0為完全不透明,改變這個值可以得到一個漸變的效果。

透明度alpha的計算。顏色在本質地上是光的產物,可以把透明度理解為玻璃的透光性。例如一個alpha=0.2的顏色,可以將其想象為透光率為80%的彩色玻璃。透過這塊玻璃看去,由于80%的光都透過了,因此留下來的顏色只剩20%,即所謂系數為0.2的alpha。

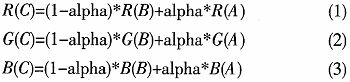

2 Matlab驗證效果

現在通過Matlab來進行兩幅圖片疊加驗證。

將alpha設為0.4和0.6的顏色進行疊加。這時相當于疊加了兩塊玻璃,一塊透光率為60%,另一塊為40%。一道光束穿過,經過60%透光率玻璃時,光線強度剩下80%,再經過40%透光率玻璃時,光線進一步被削弱,只剩下60%*40%=24%。這意味著合成的圖片有24%的透明性。

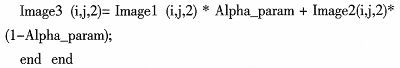

兩幅圖片的分辨率都是1 024*768,疊加后處理效果圖如下:

由效果圖可以看出,實現了海鷗在藍天白云中飛翔的半透明效果。由于藍天白云圖片alpha為0.4,海鷗圖片alpha為0.6,所以海鷗透明度明顯高于藍天白云。隨著藍天白云alpha值的提高,透明度也會提升,相反海鷗透明度會隨之降低。

雖然實現了半透明疊加效果,但由于圖片分辨率過高,Matlab要對每個像素點的RGB三通道分別進行alpha算法公式運算,最后輸出合成圖片,用了大約0.75 s的時間。對視頻圖像無法做到實時處理的效果。因此,考慮用FPGA硬件設計來實現此算法。

3 FPGA硬件實現

本設計硬件采用的市面上常用的開發板,主控芯片是ALTERA公司的Cycelone IV,并帶有VGA,百兆網口,RS232串口等一系列接口。FPGA內部產生兩幅圖片同時進行半透明化疊加,并且通過開發板上的按鍵來控制alpha系數,從而實現調節兩幅圖片的之間的透明度,最后在VGA顯示器進行顯示。

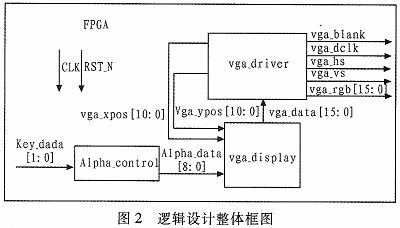

3.1 邏輯設計整體框圖

整體框圖包括3個模塊,alpha_control模塊、vga_display模塊和vga_driver模塊

alpha_control模塊:通過外部按鍵控制alpha半透明參數,實現兩幅疊加圖片之間透明度實時轉換。

vga_display模塊:由于FPGA內部的memory容量有限,無法存儲高分辨圖片,因此通過此模塊生成兩幅圖片,并實現半透明圖片的疊加,然后送到VGA顯示器進行實時顯示。

vga_driver模塊:驅動VGA[5]工作在預定的分辨率下,這里驅動顯示器工作在1024*768@65MHz的分辨率下。

3.2 VGA驅動原理

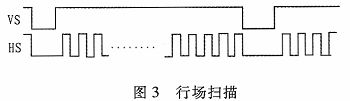

VGA驅動本質就是在一定工作頻率下,產生準確的時序關系包括:VS-垂直同步信號,HS-水平同步信號,消隱信號之間的關系。

在VGA顯示過程中,完成一行掃描所要的時間為水平掃描時間,完成一幀掃描所需要的時間稱為垂直掃描時間。每掃描完一行用行同步信號進行同步;掃描完所有行后用場同步信號進行同步。本文設計采用的是1024*768@65MHz模式。依據時序標準,每顯示行包含1344個點,其中1024為顯示有效區,320點為消隱區,每行的行同步脈沖低電平寬度為136個像素點;同理每場有806行,有效行為768,其中場同步脈沖低電平寬度為6行。

如上圖所示,每一場的掃描都包含若干個行掃描,如此往復循環。

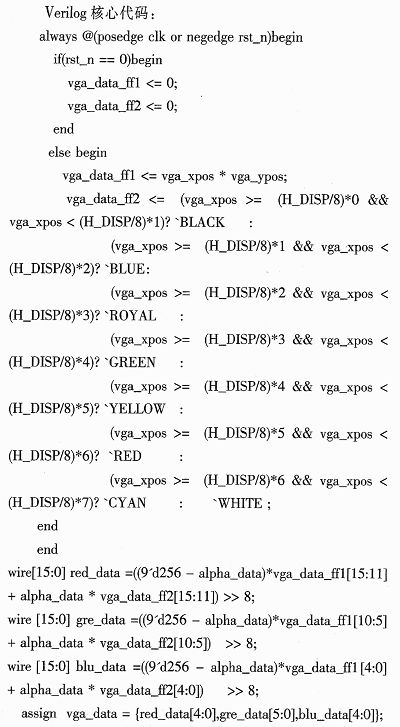

3.3 Alpha算法verilog實現

為了實現快速運算,這里將透明比例按2的N次冪來分級(Alpha=1/256),同時進行了移位算法,式(1)、式(2)、式(3)變為以下公式:

評論