基于CPLD的LCD1602顯示系統設計與實現

摘要:為了提高LCD1602顯示效果,增強抗擾能力,文章基于TOP2812開發板,依據LCD1602操作時序要求,在開發板CPLD部分實現了LCD1602顯示系統的設計。文中對LCD1602時序進行了詳細分析,并在QuartusⅡ平臺下采用Verilog HDL編寫了test bench測試文件和驅動程序,經仿真和實際測試表明,顯示效果較好,達到了設計要求。

本文引用地址:http://www.104case.com/article/201609/303571.htm關鍵詞:CPLD;LCD1602;顯示系統;時序;Vetilog HDL

隨著技術的發展,社會數字化的程度顯得越來越明顯,集成電路在社會當中的應用也越來越廣泛。傳統的ASIC曾在數字領域扮演重要角色,雖種類繁多,但功能固定、管腳有限,應用范圍也相對較窄,因此在一定程度上限制了人們對其的使用。如今,隨著現場可編程技術的發展,FPGA及CPLD技術已不再是傳統 ASCI技術領域的一個點綴與補充,其顯然已成為電子應用領域廣受歡迎的實用化技術,為數字系統的科研實驗、樣機試制、小批量產品的即時實現等提供了最佳途徑。EPM240T100C5是Altera公司生產的MaxII系列CPLD,其功耗低、價格廉、配置靈活、資源豐富,具有較高的市場性價比,因而備受青睞。

在顯示輸出方面,目前主要采用3種方式,即:圖形、數字或專用符號,在嵌入式領域,顯示常采用LED、數碼管及液晶顯示器。前兩種雖然實現簡單,但顯示內容不夠豐富。LCD1602具有體積小、功耗低、顯示容量大、接口簡單,操作方便,能夠顯示字符、數字及符號等優點,因此被廣泛應用于日常生活當中。

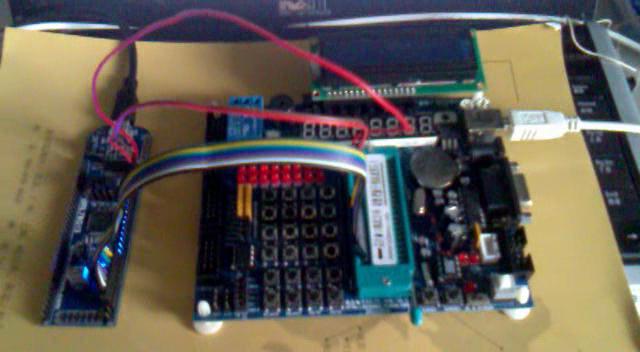

該文以EPM2405100C5為控制核心,在Quartus II平臺下采用Verilog HDL編寫LCD1602顯示驅動程序,并生成相應目標文件,最終下載至目標芯片,實現LCD1602的顯示設計功能。

1 實現原理

將EPM240T100C5的I/O口與LCD1602的數據管腳及控制管腳進行接口,利用Verilog HDL編寫軟件程序,使CPID輸出滿足LCD1602的操作時序。由于LCD1602屬慢顯示設備,而CPLD往往時鐘頻率較高,為此需要對CPLD主時鐘進行分頻,從而產生合適的時鐘信號供LCD1602使用。在讀/寫數據時,需要對LCD1602的忙標志進行檢測,只有在忙標志位為0的情況下,才能完成對數據或指令的讀取與寫入。此外,為方便對LCD1602模塊進行操作,其內部控制器為該模塊提供了11條控制指令,通過寫入相應的控制指令,可定制該模塊的顯示模式。LCD1602為用戶提供的存儲空間分3部分:DDRAM、CGRAM和CGROM。DDRAM共有80個存儲空間,對應屏幕的兩行,每行40個,但每行可顯示的地址只有16個,其他地址所寫入的數據可通過移屏進行顯示。CGRAM為用戶自定義字符圖形RAM,用戶可以定制特定的圖形。 CGROM為字符發生ROM,其內部已存儲160個不同點陣字符圖形,由于其編碼與ASC II碼基本一致,因此在進入寫操作時,也可直接寫入對應字符,如寫8’h41,可顯示字符A,直接寫入“A”,也可達到同樣的顯示效果。

LCD1602的初始化主要用于完成字符顯示模式、光標顯示模式、寫入數據后地址指針變化的設置、清屏及開顯示等操作。該模塊若要成功地被驅動,除了正確的初始化步驟以外,還必須依賴于準確的操作時序,因此分析其操作時序也就顯得尤為重要。

2 時序分析

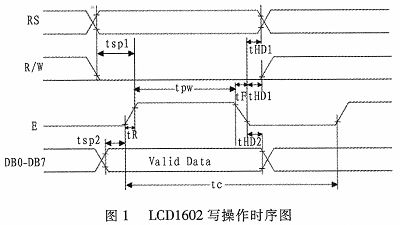

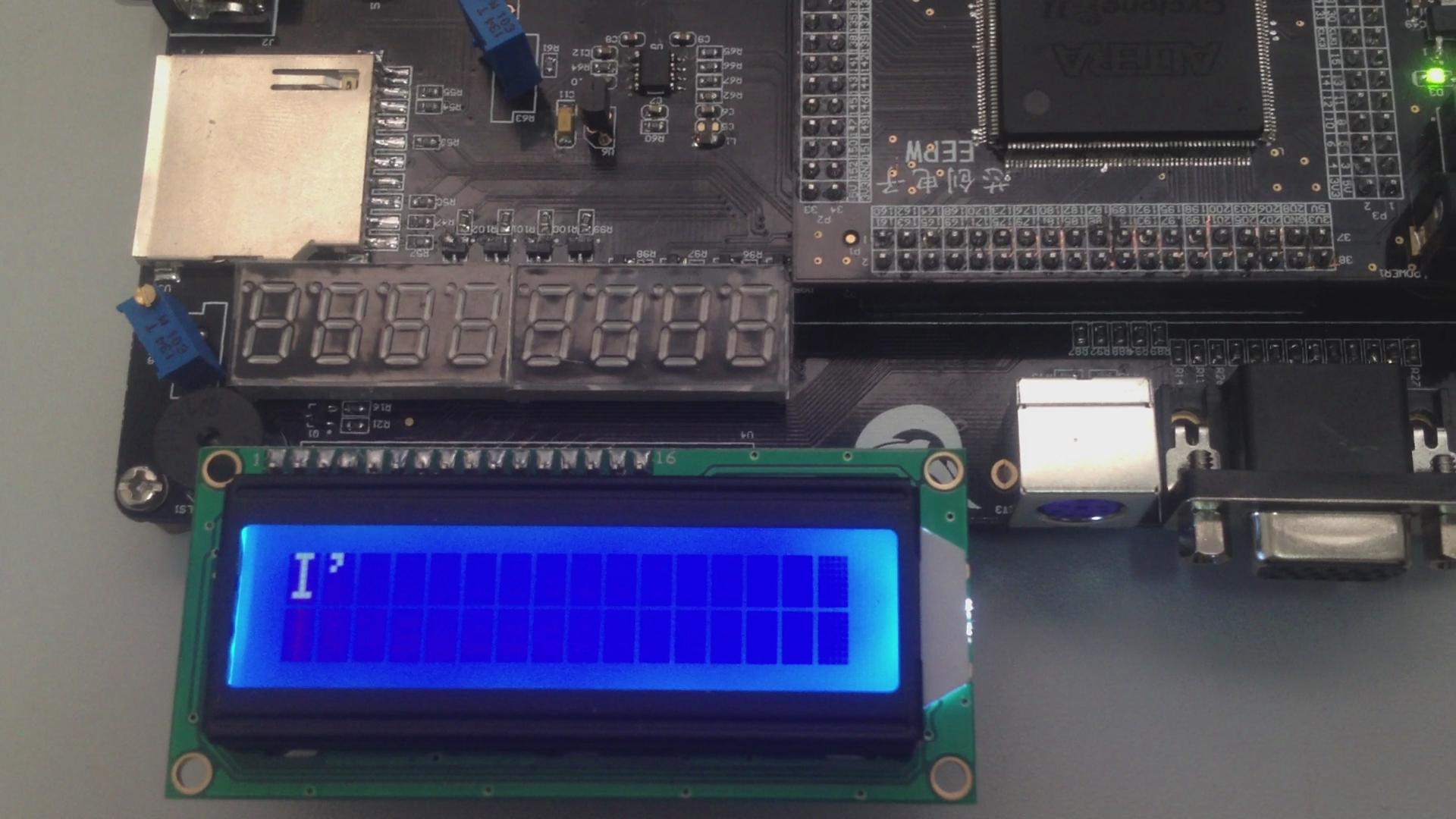

操作時序為IC芯片的工作提供了正確的節拍,如果節拍錯了,那么芯片將不可能正常工作。LCD1602的寫操作時序圖如圖1所示。

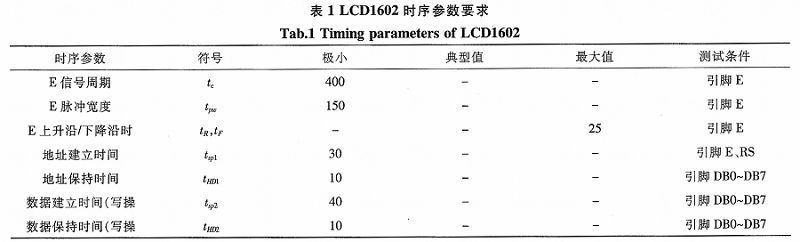

由圖1可知,若要寫入正確的數據,必須在E的上升沿到來之前建立RS及R/W電平,同時完成數據的寫入操作,在E處于高電平期間,寫入的數據才能有效。圖 1中,tsp1即為RS、R/W的建立時間,tsp2為數據的建立時間,若要正確完成寫入操作,必須使各建立時間滿足時序要求。數據在E的高電平期間有效,即持續一個脈沖寬度tpw。圖1中具體參數的時間要求如表1所示。

為方便建立E信號的波形,可取tpw=tc/2,即將E的波形設計為方波,只要保證tc>400 ns,則其高、低電平所維持的時間都將不小于200 ns,而如果將RS、R/W及數據變化的時間都取在E信號低電平的中間位置,則地址及數據的建立時間和地址及數據的保持時間都將大于100 ns,對比表1的時序參數要求,顯然按這種方法設計出的時序是完全滿足LCD1602寫操作時序要求的。

因此,只需選取一個合適的tc,也就基本確定寫操作時序了。由于LCD1602初始化時需要延時5 ms來完成對顯示模式的設定,因此可選取5 ms作為tc的取值,從而簡化顯示模塊的初始化操作。

3 軟件實現

文中設計采用Verilog HDL實現,模塊程序的接口如下所示:

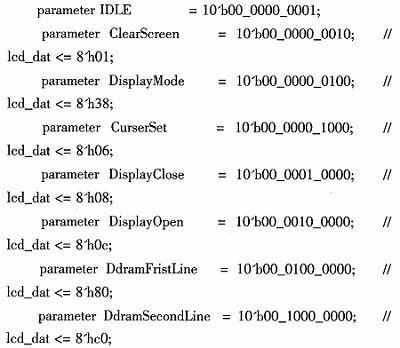

由于LCD1602初始化需要按特定步驟寫入不同的控制指令,其可顯示的數據地址在空間上是兩個獨立的固定區域,因此可借用有限狀態機的設計思想進行設計系統。狀態采用一位獨熱碼進行編碼。所定義狀態如下:

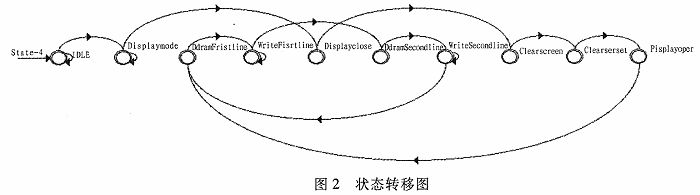

在QuartusⅡ平臺下,經綜合所得的狀態轉移關系如圖2所示。

要想實現狀態的轉移,需構建LCD1602顯示模塊所必需的時鐘,在時序分析過程中已確定將E信號的周期設計為5ms,而數據的寫入以及RS、R/W電平的變化總是在E信號低電平的中間發生,因此可重新建立一個時鐘,使其在該位置發生跳變,可以是上升沿也可以是下降沿,其周期與E信號周期相等,為便于設計,也將該時鐘設計成脈寬為50%的方波信號。這里設E信號的時鐘為lcd_en,在E信號低電平中間位置跳變的時鐘為clkjlag。若選擇 clk_flag的上升沿觸發RS、R/W電平的改變及數據的寫入操作,則顯然clk_flag高電平要超前clk_div高電平90°。為得到相位上互差90°的兩個時鐘,可以通過對系統時鐘分頻,構建一個周期為2.5ms的時鐘clk_div,使得clk_flag總是在clk_div的上升沿翻轉,而lcd_en總是在clk_div的下降沿翻轉,由此即可得到相位上互差90°的兩個時鐘信號了。由于主時鐘為30 Mhz,因此需對其進行37 500分頻,即可得到周期為2.5 ms的clk _div。其軟件實現如下:

評論