EDA技術(shù)進(jìn)行數(shù)字電路設(shè)計(jì)

數(shù)字電路設(shè)計(jì)性本身就是一種綜合性設(shè)計(jì),其設(shè)計(jì)電路中一般包含不同類型電路,在設(shè)計(jì)過(guò)程中,不可避免地存在許多錯(cuò)誤和不足如果直接按照這一設(shè)計(jì)電路在電路板上進(jìn)行安裝、調(diào)試,其結(jié)果往往使電路調(diào)試費(fèi)時(shí)費(fèi)力,甚至?xí)鹪骷蛢x器設(shè)備損壞等問(wèn)題,導(dǎo)致設(shè)計(jì)不能達(dá)到預(yù)期效果。應(yīng)用EDA技術(shù)在仿真軟件平臺(tái)上設(shè)計(jì)數(shù)字電路,能幫助熟悉和掌握最先進(jìn)電路設(shè)計(jì)方法和技能。在電子技術(shù)高速發(fā)展今天,新器件、新電路不斷涌現(xiàn),而設(shè)計(jì)條件受經(jīng)費(fèi)等因素制約,一般不能及時(shí)更新。采用軟件仿真方法,在計(jì)算機(jī)上虛擬一個(gè)先進(jìn)測(cè)試儀器、元器件品種齊全電子工作臺(tái),可進(jìn)行驗(yàn)證性、測(cè)試性、設(shè)計(jì)性等實(shí)驗(yàn)針對(duì)性訓(xùn)練,培養(yǎng)使用計(jì)算機(jī)及分析、應(yīng)用和創(chuàng)新電路能力。“以仿代實(shí)”,“以軟代硬”應(yīng)該成為當(dāng)代設(shè)計(jì)發(fā)展潮流之一。

3基于EDA技術(shù)進(jìn)行數(shù)字電路設(shè)計(jì)研究

EDA技術(shù)在數(shù)字系統(tǒng)中應(yīng)用以基于AlteraEPM7128SLC84-15芯片和MAX PlusII 10.0軟件平臺(tái)數(shù)字鐘設(shè)計(jì)為例,討論EDA技術(shù)在數(shù)字系統(tǒng)中具體應(yīng)用。

3.1 EDA技術(shù)設(shè)計(jì)流程

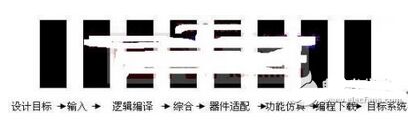

在設(shè)計(jì)方法上,EDA技術(shù)為數(shù)字電子電路設(shè)計(jì)領(lǐng)域帶來(lái)了根本性變革,將傳統(tǒng)“電路設(shè)計(jì)硬件搭試調(diào)試焊接”模式轉(zhuǎn)變?yōu)樵谟?jì)算機(jī)上自動(dòng)完成,如圖1所示。

圖1:設(shè)計(jì)流程

3.2設(shè)計(jì)要求

具有時(shí)、分、秒、計(jì)數(shù)顯示功能,以24小時(shí)循環(huán)計(jì)時(shí)。具有清零和調(diào)節(jié)小時(shí)、分鐘功能。具有整點(diǎn)報(bào)時(shí)功能。

3.3輸入設(shè)計(jì)源文件

一個(gè)設(shè)計(jì)項(xiàng)目由一個(gè)或多個(gè)源文件組成,它們可以是原理圖文件、硬件描述語(yǔ)言文件、混合輸入文件,點(diǎn)擊Source/New菜單,選擇你所要設(shè)計(jì)源文件類型,進(jìn)入設(shè)計(jì)狀態(tài),完成源文件設(shè)計(jì),存盤(pán)、退出;另在一張?jiān)韴D編輯器窗口中,通過(guò)File/Matching Symbol菜單,建立一張?jiān)韴D符號(hào),生成一個(gè)與原理圖文件相同名、相同功能邏輯宏元件,它自動(dòng)加到元件列表中,可以在更高層圖紙中反復(fù)調(diào)用;

3.3邏輯編譯

邏輯編譯選擇器件EPM7128SLC84-15,使用MAX PlusⅡ編譯器編譯設(shè)計(jì)項(xiàng)目,通過(guò)編譯器自動(dòng)進(jìn)行錯(cuò)誤檢查、網(wǎng)表提取、邏輯綜合、器件適配,最終產(chǎn)生器件編程文件(。jed)。

3.4綜合

綜合就是利用EDA軟件系統(tǒng)綜合器將VHDL軟件設(shè)計(jì)與硬件可實(shí)現(xiàn)性掛鉤,這是將軟件轉(zhuǎn)化為硬件電路關(guān)鍵步驟。綜合器對(duì)源文件綜合是針對(duì)某一 FPGA/CPI D供應(yīng)商產(chǎn)品系列。因此,綜合后結(jié)果具有硬件可實(shí)現(xiàn)性。EDA提供了良好邏輯綜合與優(yōu)化功能,它能夠?qū)⒃O(shè)計(jì)人員設(shè)計(jì)邏輯級(jí)電路圖自動(dòng)地轉(zhuǎn)換為門(mén)級(jí)電路,并生成相應(yīng)網(wǎng)表文件、時(shí)序分析文件和各種報(bào)表,若設(shè)計(jì)沒(méi)有錯(cuò)誤,最終可生成可以編程下載。sof文件。

3.5器件適配

綜合通過(guò)后必須利用FPGA/CPLD布局/布線適配器將綜合后網(wǎng)表文件針對(duì)某一具體目標(biāo)器件進(jìn)行邏輯映射操作,其中包括底層器件配置、邏輯分割、邏輯優(yōu)化、布局布線等操作。適配后產(chǎn)生時(shí)序仿真用網(wǎng)表文件和下載文件,如JED或POF文件。適配對(duì)象直接與器件結(jié)構(gòu)細(xì)節(jié)相對(duì)應(yīng)。

3.6功能仿真

通常,在設(shè)計(jì)過(guò)程中每一個(gè)階段都要進(jìn)行仿真驗(yàn)證其正確性。在綜合前,要進(jìn)行行為仿真,將VHDI源程序直接送到VHDI仿真器中仿真,此時(shí)仿真只是根據(jù)VHDI語(yǔ)義進(jìn)行,與具體電路沒(méi)有關(guān)系。綜合后,可利用產(chǎn)生網(wǎng)表文件進(jìn)行功能仿真,以便了解設(shè)計(jì)描述與設(shè)計(jì)意圖一致性。功能仿真僅對(duì)設(shè)計(jì)描述邏輯功能進(jìn)行測(cè)試模擬,以了解其實(shí)現(xiàn)功能是否滿足原設(shè)計(jì)要求,仿真過(guò)程不涉及具體器件硬件特性,如延遲特性。時(shí)序仿真根據(jù)適配后產(chǎn)生網(wǎng)表文件進(jìn)行仿真,是接近真實(shí)器件運(yùn)行仿真,仿真過(guò)程中已將器件硬件特性考慮進(jìn)去了,因此仿真精度要高得多。時(shí)序仿真網(wǎng)表文件中包含了較為精確延遲信息。

3.7編程下載

通過(guò)仿真確定設(shè)計(jì)基本成功后,即可通過(guò)Byteblaster下載電纜線將設(shè)計(jì)項(xiàng)目以JTAG方式下載到器件中,完成設(shè)計(jì)所有工作。通過(guò)此例設(shè)計(jì)流程講述可知,EDA技術(shù)及其工具在數(shù)字電路系統(tǒng)(包括模擬電路系統(tǒng))中正發(fā)揮著越來(lái)越重要作用,其應(yīng)用深度和廣度正在向更深層次延伸。

3.8目標(biāo)系統(tǒng)

用VHDL語(yǔ)言描述編碼電路。譯碼電路用CASE語(yǔ)句完成查表譯碼,其中有近4O種可能情況。通過(guò)求出伴隨式值,把有一個(gè)錯(cuò)誤數(shù)據(jù)取反糾正過(guò)來(lái),其他情況給出信號(hào),指出有錯(cuò)誤。編譯碼電路選用ALTERA公司生產(chǎn)器件EPF1OK10TC144-3,其中編碼電路占用了32個(gè)邏輯單元,譯碼電路占用了 163個(gè)邏輯單元。對(duì)編碼譯碼電路做功能仿真。測(cè)試使用看來(lái),當(dāng)數(shù)據(jù)輸人全為‘1‘,如果總線上傳來(lái)數(shù)據(jù)最后一位出錯(cuò)。為‘0’,正確數(shù)據(jù)異或而成數(shù)據(jù)檢查線DC使得譯碼器能把最后一位改為‘1’;如數(shù)據(jù)輸人是“00000001”,編碼器DC為“19”而一旦出現(xiàn)兩個(gè)錯(cuò)誤。如最高位和最低位,譯碼器指示是不可糾正錯(cuò)誤;如數(shù)據(jù)正確傳輸,譯碼器指示沒(méi)有錯(cuò)誤。

4本文作者創(chuàng)新點(diǎn)

目前,現(xiàn)代集成電路技術(shù)發(fā)展使以現(xiàn)場(chǎng)可編程門(mén)陣列為代表大容量可編程邏輯器件等效門(mén)數(shù)迅速提高,其規(guī)模直逼標(biāo)準(zhǔn)門(mén)陣列,達(dá)到了系統(tǒng)集成水平。特別是進(jìn)入二十世紀(jì)90年代后,隨著CPLD、FPGA等現(xiàn)場(chǎng)可編程邏輯器件逐漸興起,VHDL、Verilog等通用性好、移植性強(qiáng)硬件描述語(yǔ)言普及,ASIC 技術(shù)不斷完善,EDA技術(shù)在現(xiàn)代數(shù)字系統(tǒng)和微電子技術(shù)應(yīng)用中起著越來(lái)越重要作用。從通常意義上來(lái)說(shuō),現(xiàn)代電子系統(tǒng)設(shè)計(jì)已經(jīng)再也離不開(kāi)EDA技術(shù)幫助了。

評(píng)論