研究人員為IoT打造開放源碼的處理器核心

蘇黎世聯邦理工學院(ETH Zurich)與義大利波隆納大學(University of Bologna)的研究人員共同開發出一款開放源碼的處理器PULPino,專為低功耗的穿戴式裝置與物聯網(IoT)應用最佳化。

本文引用地址:http://www.104case.com/article/201604/289262.htm開放源碼和協同開發是當今軟體世界的標準作法,例如Linux。盡管也有一些像OpenRISC與Opencores等硬體計劃,開放源碼的硬體在板級開發時更能取得較大動能。例如Arduino與Raspberry Pi的PCB設計可公開取得。然而,這些開發板上所采用的晶片仍然是專有的。

如今,這支由ETH Zurich教授Luca Benini帶領的研究團隊已將其微處理器系統的一項完整設計公開在公共領域了,這就是PULP計劃(平行超低功耗)的衍生系統。

32位元的PULPino是專為以電池供電的超低功耗裝置而設計,其算術指令也是開放源碼的:研究人員們打造的這款處理器可相容于加州大學柏克萊分校(UC Berkeley)所開發的RISC-V開放源碼指令集。

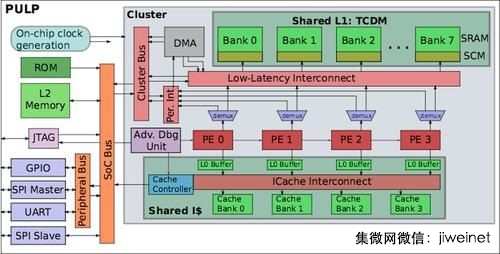

PULP采用4 核心的處理器設計

PULPino是更通用的PULP之簡化版,內建單一處理元素以取代4處理元素叢集,而且也簡化了指令與資料RAM,并于2015年時采用FPGA建置。根據官網的簡報資料,PULPino核心稱為RI5CY,是一種RISC-V的4階循序管線建置。

研究人員開發的處理器核心可媲美ARM Cortex-M4核心,擁有趨近于1 的每周期數指令集,支援基礎整數指令集(RV32I)、壓縮指令集(RV32C)以及部份支援乘法指令集擴展(RV32M)。它為硬體回路建置了非標準擴展、后遞增加載與儲存指令集、ALU與MAC作業。為了執行FreeRTOS等嵌入式作業系統,并支援特權規格子集。當核心閑置時,該平臺可切換至低功耗模式,在出現事件/中斷時僅啟動單一事件單元并喚醒核心作業。

PULP四核心IC采用Globalfoundries的28nm制程,已于2015年11月投片;首批ULPino核心設計則在2016年1月采用聯電(UMC)的65nm CMOS制程投片。PULPino平臺可用于RTL模擬,實現FPGA與SoC。擁有完整的除錯支援,包括FreeRTOS;作業于400MHz時脈頻率與1.2V的電壓,晶片功耗約32.8mW。

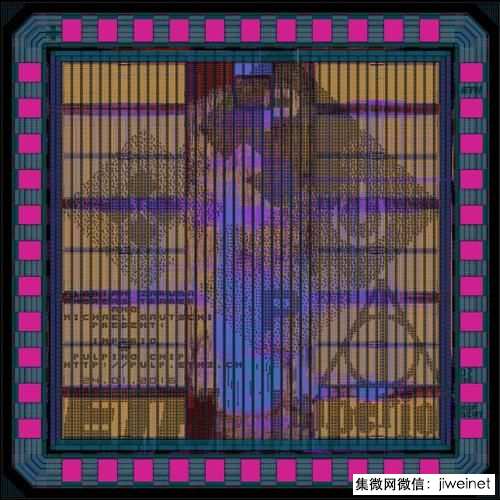

PULPino (Imperio)晶片圖

根據研究人員表示,使用PULPino的授權將會“十分寬松”,而且也與正開發中的另一開放源碼處理器lowRISC一致。

“從最近許多開放源碼硬體的例子來看,使用權經常受到獨家銷售權與非競爭條款的限制,”Benini說,“但我們開發的系統并未針對授權附加任何限制條件。”

研究人員預計,PULPino可以用來驅動智慧手表、監測生理功能的感測器或物聯網傳感器。 PULPino目前已經用于瑞士與歐洲研究機構的其他研究計劃,以及英國劍橋大學(Cambridge University)。

Benini認為,歐洲的中小企業(SME)應該也會對PULPino感興趣,因為他們經常無法負擔開發ASIC的成本。透過開放來源的免授權費設計,可望大幅降低開發成本,從而使SME與ETH受惠。

評論