歐盟為5G打造III-V族CMOS技術

歐盟(E.U.)最近啟動一項為期三年的“為下一代高性能CMOS SoC技術整合III-V族奈米半導體”(INSIGHT)研發計劃,這項研發經費高達470萬美元的計劃重點是在標準的互補金屬氧化物半導體 (CMOS)上整合III-V族電晶體通道。其最終目的則在于符合未來的5G規格要求,以及瞄準頻寬更廣、影像解析度更高的雷達系統。

本文引用地址:http://www.104case.com/article/201603/287926.htm除了IBM (瑞士),該計劃將由德國弗勞恩霍夫應用固態物理研究所Fraunhofer IAF、法國LETI、瑞典隆德大學(Lund University)、英國格拉斯哥大學(University of Glasgow)以及愛爾蘭丁鐸爾國家研究所(Tyndall National Institute)等組織聯手進行。

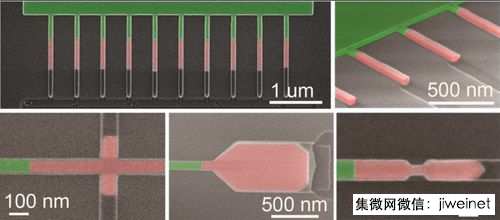

采用IBM模板輔助選擇性外延(TASE)技術制造的單晶結構圖——矽晶部份是綠色,III-V族半導體以紅色表示

(來源:IBM)

以IBM與隆德大學為主導的這項計劃可分為兩個階段,IBM專注于傳統平面電晶體原型與III-V族通道,而隆德大學則將深入研究垂直III-V族電晶體通道的可用性。

“首先,合作夥伴們將先共同確定水平或垂直電晶體原型是否最具有遠景,”IBM的科學家Lukas Czornomaz介紹,“接著,我們將聯手在三年計劃屆滿以前推出一款射頻(RF)測試電路,例如功率放大器(PA)。”

IBM 有信心其平面方法將可發揮效用,因為該公司已經在一份去年發表的研究報告(該報告主題為IBM Scientists Present III-V Epitaxy and Integration to Go Below 14nm)中證實了這一途徑在14nm及其后的可行性。

IBM 的制程途徑是透過其所謂的“模板輔助選擇性外延”(TASE)技術。研究人員在矽基板上得以相容前閘極(gate-first) CMOS的理想III-V族電晶體通道所在位置生長氧化物銅絲。接著再用III-V材料涂布奈米線,使其僅在1奈米級或埃級的區域接觸基板。最后,研究人 員從III-V涂布奈米線內部移去氧化層,因而使III-V族奈米管電晶體通道準確地位于正確位置。

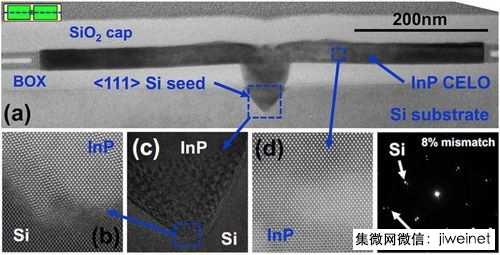

(a)采用IBM技術整合于矽晶上的III-V族半導體橫截面圖。由堆疊斷層組成的晶種區(b,c)存在較多缺陷,而遠離晶種區域可觀察到完美晶格結構——未與矽晶匹配的部份僅8%,呈現完全松弛的III-V結構(d,e)

IBM預期,毫米波(mmWave)的RF性能功耗水準比目前更低得多,不僅可用于促進5G進展,同時還可用于認知電腦、下一代物聯網(IoT)以及基于云端的支援平臺。

INSIGHT 計劃的既定目標在于使CMOS擴展到超越7nm節點以后,從而開啟一個以超高性能SoC服務為基礎的全新應用范圍。除了IBM與隆德大學,包括 Fraunhofer、LETI、格拉斯哥大學與丁鐸爾國家研究所等其他合作夥伴也分別為這項計劃貢獻在III-V族CMOS方面的專業知識與技術。

評論