一種創新的晶圓級熱載子并行測試方法

引言

隨著VLSI集成度的日益提高,MOS器件尺寸不斷縮小至亞微米乃至深亞微米,熱載子效應已成為最嚴重的可靠性問題之一。現今,為了降低成本,減少周期,不斷的提高工藝,晶圓級的器件可靠性測試愈來愈被廣泛的應用。縱觀許多晶圓級的器件可靠性測試,相對于其他器件可靠性測試項目如前端的TDDB、Vramp、Jramp及后端的恒溫電遷移測試的測試時間,熱載子效應測試需要花費的時間更長。當務之急是怎樣縮短熱載子效應測試周期。

為了縮短測試周期,有些公司采用對器件施加更高的HCI應力條件來加速器件的退化,但是這種方式并不看好,因為在更高的HCI應力條件下,器件的物理機制已發生了變化。在我們想要解決周期過長的問題前,我們先參考封裝級的熱載子效應測試。在封裝級的熱載子效應測試中,有一種測試板可以支持幾個器件同時進行測試。如果我們仿照這種封裝級的熱載子效應測試,把它應用在晶圓級,那晶圓級的熱載子效應測試周期將會大大的縮短。

實驗

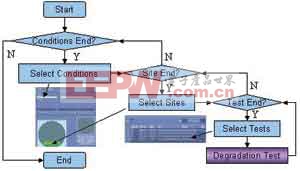

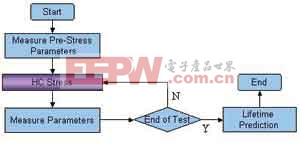

傳統的晶圓級熱載子效應測試程序(PDQ-WLR,版本3.01[2])是由美國Sandia Technologies inc.公司提供的,在Agilent 4072自動控制測試機臺上完成測試。它的測試流程是用HCI_4_MOS_Builder生成兩個設置文件,一個是參數施加命令文件,另一個是完成施加HCI應力條件的時間讀點文件,并且按照圖1所描述的測試流程來完成測試。由于商業要求,這套程序是被打包,不可改變的。

傳統的晶圓級熱載子效應測試程序(PDQ-WLR,版本3.01[2])是由美國Sandia Technologies inc.公司提供的,在Agilent 4072自動控制測試機臺上完成測試。它的測試流程是用HCI_4_MOS_Builder生成兩個設置文件,一個是參數施加命令文件,另一個是完成施加HCI應力條件的時間讀點文件,并且按照圖1所描述的測試流程來完成測試。由于商業要求,這套程序是被打包,不可改變的。

圖1a 熱載子效應測試總流程

圖1b 熱載子效應退化的應力施加及電性參數測試流程

傳統的晶圓級熱載子效應測試是一個器件一個器件的被施加HCI應力條件。測試的總時間是根據測試器件的個數,不同的HCI應力條件個數,以及不同HCI應力條件下實際應力施加的時間的總和來計算。例如,熱載子效應測試有3種不同的HCI應力條件,每種HCI應力條件要有3個器件來做樣本,每次要施加HCI應力條件10 000秒,再加上器件退化后所要測量的特性參數的時間,總的測試時間要花費大約27小時——27=3*3*(1000+10000)/3600)。這個時間是一種類型器件完成一次的時間,例如NMOS晶圓級熱載子效應的測試時間,如果是幾種不同類型的器件,相應的時間將是成倍的增加。從圖1a(熱載子測試的總流程),和圖1b(熱載子效應退化的應力施加及電性參數測試流程),我們很清楚的可以算出超過90%的時間是用在施加HCI應力條件使器件退化的時間上。所以我們開發了一套程序來實現對一組同樣類型的器件進行并行施加HCI應力條件,以此取代傳統的串聯方式的一個器件一個器件施加HCI應力條件及參數測試的流程。

人們也曾試著改變版圖的器件連接方式,例如將幾個器件需要施加HCI應力條件的端口(柵極或漏極)連接在一起,這樣一來,用傳統的由美國Sandia Technologies inc.公司提供的程序也可以同時施加HCI應力條件在幾個器件上。但由于從同一個施加HCI應力的端口到幾個器件的連線長短不同造成的寄生電阻,使得一小部分HCI應力壓降會損失在這些連線上,最終導致這幾個器件實際被施加的HCI應力不一致,造成誤差。圖2a和圖2b顯示了在版圖上改變器件的連接方式。

閱讀全文請點擊下載PDF和在線閱讀>>

http://www.epc.com.cn/free_test/index_new.htm

評論