基于FPGA的RS編碼器的設(shè)計與實現(xiàn)

本文引用地址:http://www.104case.com/article/192144.htm

4 RS編碼器的仿真

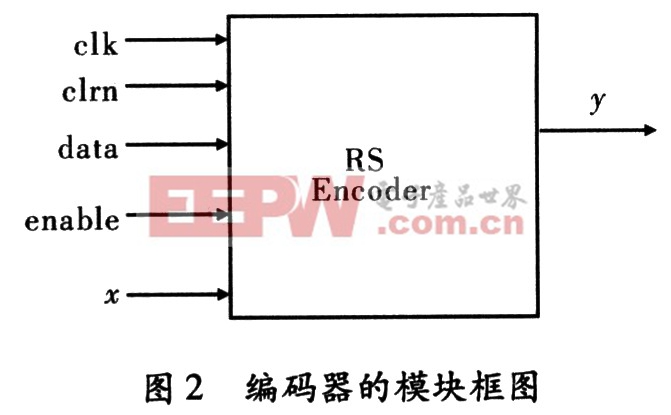

本設(shè)計是實現(xiàn)了RS(15,9)的編碼,本設(shè)計編碼器的模塊框圖,如圖2所示。

各信號說明如下:

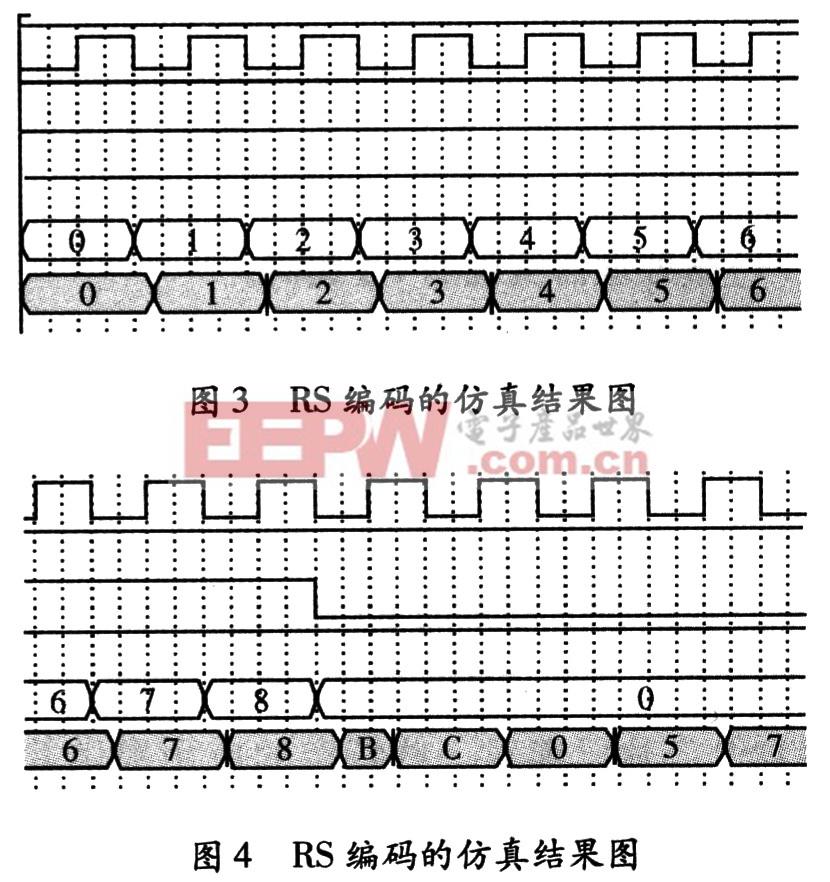

本設(shè)計信號時鐘clk周期是40 ns,clrn是復(fù)位號,data表示信息輸入有效,enable表示啟動編碼器,開始編碼,x是4 bit信息符號,y是編碼生成的4 bit碼字。由下圖編碼圖形可知,一次編碼周期需要590.0 ns,最大編碼速率為l700 MHz。因此,一次編碼需要15個時鐘周期。在25 MHz的時鐘下,RS編碼器仿真時序圖,如圖3和圖4所示,并由仿真圖可看出,本算法的編碼速度高時延間隔不到半個周期。

RS編碼測試數(shù)據(jù)如下:

輸入信息:0,1,2,3,4,5,6,7,8;

編碼器輸出:0,1,2,3,4,5,6,7,8,B,C,0,5,7。

5 結(jié)束語

RS編碼的所有運算都是建立在有限域的基礎(chǔ)上的,其中乘法器的設(shè)計是其編碼技術(shù)的關(guān)鍵。本設(shè)計實現(xiàn)了RS(15,9)的編碼設(shè)計和仿真,仿真輸出結(jié)果與理論分析一致,基于相同的原理,可以實現(xiàn)任意數(shù)據(jù)塊長度的RS編碼器設(shè)計。

評論