一種基于FPGA并行流水線的FIR濾波器設(shè)計(jì)方案

3 模塊設(shè)計(jì)

設(shè)計(jì)的FIR濾波器由10個(gè)小VHD文件和一個(gè)總體BDF文件組成,VHD文件可以分為以下三種模塊:寄存器、加法器、乘法器。

3.1 寄存器設(shè)計(jì)

寄存器用于寄存一組二值代碼,對(duì)寄存器的觸發(fā)器只要求它們具有置1、置0的功能即可,因而本設(shè)計(jì)中用D觸發(fā)器組成寄存器,實(shí)現(xiàn)寄存功能。

在CP正跳沿前接受輸入信號(hào),正跳沿時(shí)觸發(fā)翻轉(zhuǎn),正跳沿后輸入即被封鎖。

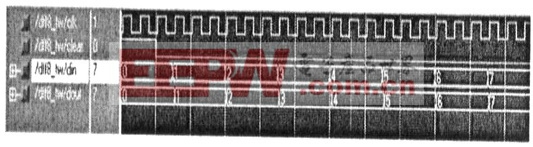

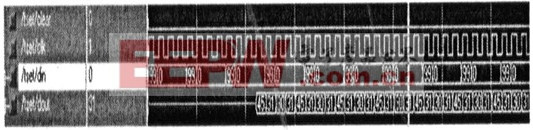

寄存器的波形仿真

3.2 加法器

在將兩個(gè)多位二進(jìn)制數(shù)相加時(shí),除了最低位以外,每一位都應(yīng)該考慮來(lái)自低位的進(jìn)位,即將兩個(gè)對(duì)應(yīng)位的加數(shù)和來(lái)自低位的進(jìn)位3個(gè)數(shù)相加。這種運(yùn)算稱為全加,所用的電路稱為全加器。

實(shí)現(xiàn)兩個(gè)二進(jìn)制數(shù)字的相加運(yùn)算。當(dāng)?shù)竭_(dá)時(shí)鐘上升沿時(shí),將兩數(shù)輸入,運(yùn)算,輸出結(jié)果。

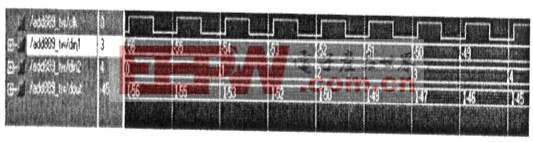

加法器的波形仿真

3.3 乘法器

從資源和速度考慮,常系數(shù)乘法運(yùn)算可用移位相加來(lái)實(shí)現(xiàn)。將常系數(shù)分解成幾個(gè)2的冪的和形式。下例為乘4c電路設(shè)計(jì)。實(shí)現(xiàn)輸入帶符號(hào)數(shù)據(jù)與固定數(shù)據(jù)兩個(gè)二進(jìn)制數(shù)的乘法運(yùn)算。當(dāng)?shù)竭_(dá)時(shí)鐘上升沿時(shí),將兩數(shù)輸入,運(yùn)算,輸出結(jié)果。

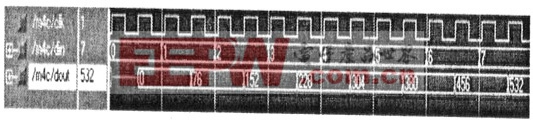

乘法器的波形仿真

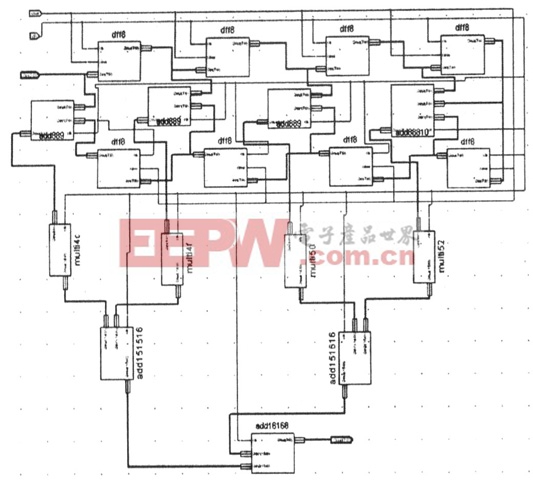

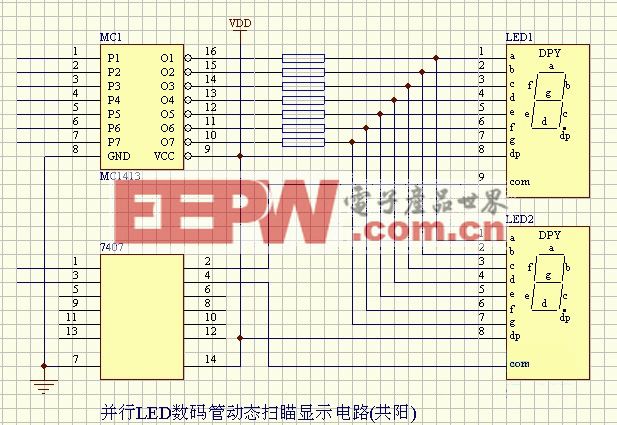

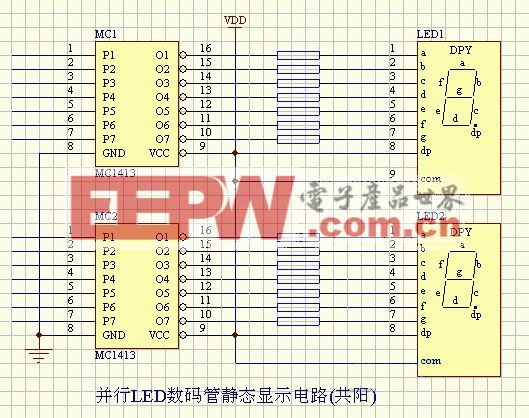

4 FIR濾波器整體電路

FIR濾波器的整體電路基本與其原理圖類似。整體電路如下圖所示:

5 FIR濾波器整體電路仿真結(jié)果

當(dāng)輸入為信號(hào)為[99,0,0,0,99,0,0,0,99,O,0,0,99。…]濾波器的實(shí)際仿真波形見(jiàn)下圖:

因?yàn)樵摓V波器為九階,信號(hào)通過(guò)各級(jí)觸發(fā)器,加發(fā)器乘法器的總延遲為13個(gè)時(shí)鐘周期,故在仿真中前13個(gè)時(shí)鐘周期沒(méi)有信號(hào)輸出。通過(guò)matl ab對(duì)濾波器進(jìn)行仿真得出的理論輸出序列為:[33,28,34,50,33,28,34,50,33,28,34,50,33,28,34,50…….]與實(shí)際仿真波形比較,波形基本一致,但是因?yàn)樵摓V波器只有九階,所以與理論值有一定誤差。

評(píng)論