一種基于FPGA并行流水線的FIR濾波器設計方案

1 Fir濾波器原理

有限沖激響應(FIR)數字濾波器和無限沖激響應(IIR)數字濾波器廣泛應用于數字信號處理系統中。IIR數字濾波器方便簡單,但它相位的非線性,要求采用全通網絡進行相位校正,且穩定性難以保障。FIR濾波器具有很好的線性相位特性,使得它越來越受到廣泛的重視。FIR數字濾波器是一個線性時不變系統(LTI),N階因果有限沖激響應濾波器可以用傳輸函數H(z)來描述,

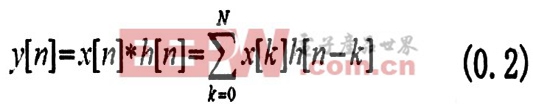

在時域中,上述有限沖激響應濾波器的輸入輸出關系如下:

其中,x[n]和y[n]分別是輸入和輸出序列。

N階有限沖激響應濾波器要用N+1個系數描述,通常要用N+1個乘法器和N個兩輸入加法器來實現。乘法器的系數正好是傳遞函數的系數,因此這種結構稱為直接型結構,可通過式(1.2)來實現

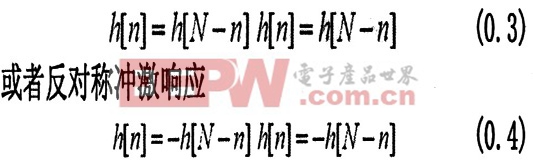

當沖擊響應滿足下列條件時,FIR濾波器具有對稱結構,為線性相位濾波器:

這種對稱性,可使得乘法器數量減半:對n價濾波器,當n為偶數時,乘法器的個數為n/2個;當n為奇數時,乘法器的個數為(n+1)/2個。在電路實現中,乘法器占用的邏輯單元數較多。乘法器的增加,意味著電路成本增加,另外對電路的工作速度也有影響。

N階線性相位的因果FIR系統的單位沖激響應濾波器可用對稱沖激響應

來描述。

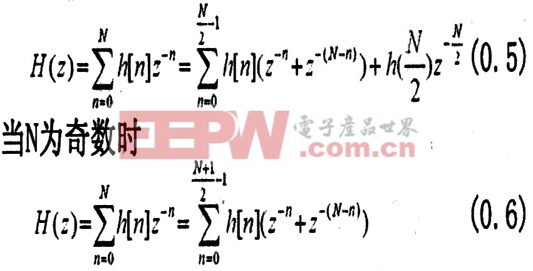

具有對稱沖激響應的FIR傳輸函數的沖激響應可寫成如下形式:

當N為偶數時

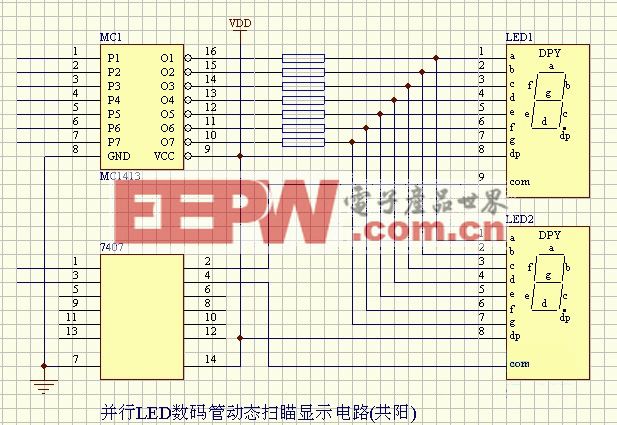

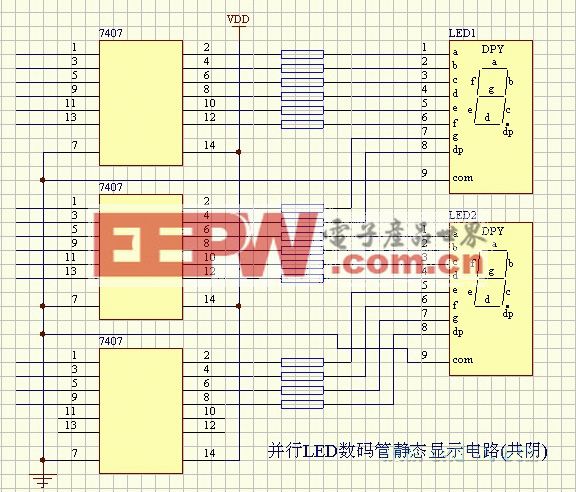

則FIR線性相位系統的結構可轉化成如圖1(a)和圖1(b)所示。

2 濾波器設計方案、

隨著數字技術日益廣泛的應用,以現場可編程門陣列(FPGA)為代表的ASIC器件得到了迅速普及和發展,器件集成度和速度都在高速增長。FPGA既具有門陣列的高邏輯密度和高可靠性,又具有可編碼邏輯器件的用戶可編程特性,可以減少系統設計和維護的風險,降低產品成本,縮短設計周期。

分布式算法是―種以實現乘加運算為目的的運算方法。它與傳統算法實現乘加運算的不同在于執行部分積運算的先后順序不同。簡單地說,分布式算法在完成乘加功能時是通過將各輸入數據每一對應位產生的部分積預先進相加形成相應部分積,然后在對各部門積進行累加形成最終結果,而傳統算法是等到所有乘積產生之后再進行相加來完成乘加運算的。與傳統算法相比,分布式算法可極大地減少硬件電路規模,很容易實現流水線處理,提高電路的執行速度。

評論