一種基于FPGA并行流水線的FIR濾波器設計方案

FPGA有著規整的內部邏輯塊陣列和豐富的連線資源,特別適合細粒度和高并行度結構特點的數字信號處理任務,如FIR、FFT等。利用FPGA實現FIR濾波器的設計過程,并且對設計中的關鍵技術一分布式算法進行詳細描述。

FIR濾波器的結構主要是非遞歸結構,沒有輸出到輸入的反饋。并且FIR濾波器很容易獲得嚴格的線性相位特性,避免被處理信號產生相位失真。而線性相位體現在時域中僅僅是h(n)在時間上的延遲,這個特點在圖像信號處理、數據傳輸等波形傳遞系統中是非常重要的。此外,他不會發生阻塞現象,能避免強信號淹沒弱信號,因此特別適合信號強弱相差懸殊的情況。

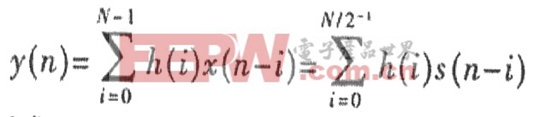

通常采用窗函數設計FIR濾波器方法簡單,但是這些濾波器的設計還不是最優的。首先通帶和阻帶的波動基本上相等,另外對于大部分窗函數來說,通帶內或阻帶內的波動不是均勻的,通常離開過渡帶時會減小。若允許波動在整個通帶內均勻分布,就會產生較小的峰值波動。對于線性相位因果FIR濾波器,它的系列具有中心對稱特性,即h(i)=±h(N一1一i)。令s(i)=x(i)±x(N一1一i),對于偶對稱,代入式(1)可得:本文引用地址:http://www.104case.com/article/192107.htm

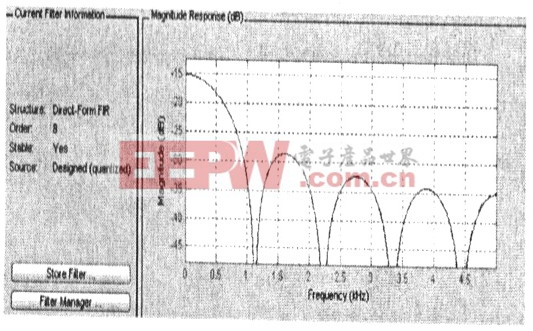

根據要求,要設計一個輸入8位,輸出8位的9階線性相位FIR濾波器,所以采用圖2(a)的方式,其中輸入信號范圍為:[99,0,0,O,99,O,0,0,99,O,0,0,99,…],此濾波器Fs為lOOkHz,Fc為10kHz。利用MATLAB設計計算9階FIR濾波器系數和幅頻響應如下:

整數化后,可得FIR濾波器的參數為:[4c,4f,50,52,52,52,50,4f,4c:]

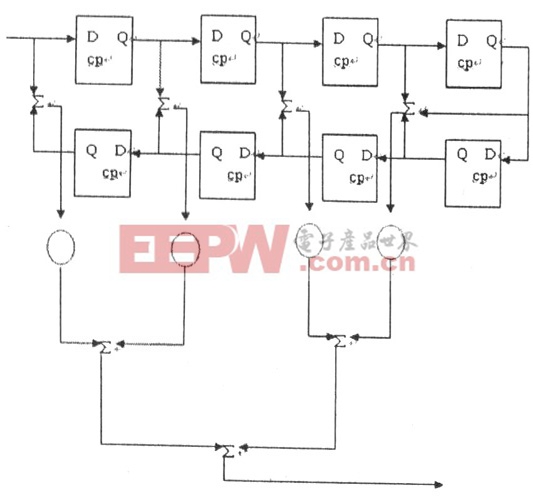

根據以上所說的思路,可以將FIR濾波器的原理圖設計如下:

下面對各加法器乘法器的輸出位數進行分析,對第一級加法器,輸入為8位,輸出統一為9位,最后一個加法器為三輸入端,輸入都為8位,輸出為10位。對各個乘法器進行分析,第一個乘法器為4c,因此輸入為9位,輸出為15位。第二個乘法器為4f,輸入為9位,輸出為15位。第三個乘法器為50,輸入為9位,輸出為15位。第四個乘法器為52,輸入為10位,輸出為16位。乘法器輸出結果兩兩相加,第一個加法器輸入都為15位,輸出為16位,第二個加法器,輸入分別為15位和16位,輸出為16位。最后這兩路輸出之和為16位。將后8位舍去,然后相加,總輸出為8位。至此,所有器件的輸入輸出都已經判定。下面進入模塊設計階段。

評論