解讀FPGA設計的安全性

TransFR是一種同時使用基本任務編程和邊界掃描單元的技術。基本任務編程修改非易失存儲器的內容(內部的或外部的) ,以便使FPGA的SRAM部分繼續(xù)工作。萊迪思的FPGA擁有可以取樣和預加載的邊界掃描單元,可以在編程時控制FPGA的I/O。

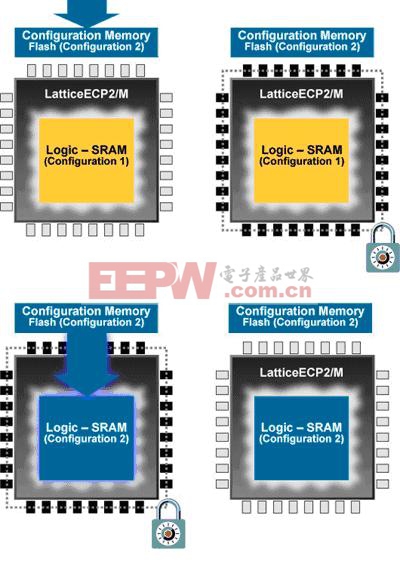

圖6 執(zhí)行TransFR的4個步驟

執(zhí)行TransFR的4個步驟:

1,進行基本任務編程。系統(tǒng)對FPGA的非易失性存儲器再編程,但不會中斷SRAM的功能。

2,可以鎖定I/O的狀態(tài),用戶可以保持或預先確定I/O的狀態(tài)。在整個重新配置過程中,I/O的值保持不變,以防止系統(tǒng)被關閉。

3, 接著用JTAG命令把新的配置傳輸至非易失存儲器。一完成對SRAM就執(zhí)行全局復位,以便使該器件處于一個已知的狀態(tài)。然后釋放I/O的狀態(tài),并再次鎖定PLL。

4,釋放輸出,內部邏輯停止對I/O的監(jiān)測。

要使用TransFR,需要用到ispLEVER開發(fā)工具和ispVM。

用戶通過使用128位AES密鑰加密文件和Lattice TransFR技術完成了更新過程,但仍有可能因為系統(tǒng)本身的弱點或違法行為引發(fā)系統(tǒng)故障。雖然FPGA的位流是加密的,但是非法操作或傳輸中的錯誤都可能損壞它,從而導致FPGA被阻塞,使系統(tǒng)無法正確地重啟。為了解決這個問題,萊迪思推出了“雙引導 ”功能。

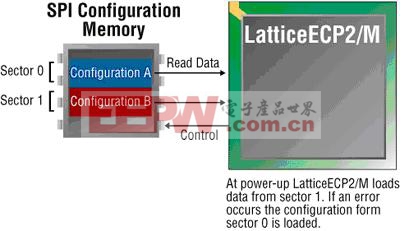

雙引導配置

在配置存儲器中存儲兩個編程文件。

圖7 雙引導配置

激活PROGRAM引腳或啟動JTAG刷新指令后,F(xiàn)PGA下載存儲在Sector 1的位流 。如果CRC出錯,F(xiàn)PGA自動恢復到Sector 0配置。Lattice XP2非易失FPGA也有此功能。該Flash元件擁有主動配置,還有一個用來存放安全( “golden” )配置的SPI Flash。

萊迪思擁有許多能幫助設計人員保障設計安全的產品。Lattice ECP2/M FPGA是一款擁有128位AES密鑰的高安全性器件。這些經(jīng)濟的器件提供了大存儲容量(高達5.3 Mbit)、高速I/O和SERDES 。非易失性LatticeXP2 FPGA是市場上一款很獨特的器件,它有著極高的安全性。由于采用了FlexiFlash技術,位流存儲在器件的Flash中, 并由128位AES密鑰對它進行保護。此外, TransFR更是保障了絕對安全的遠程系統(tǒng)更新。

設計的安全性應該是設計過程的一部分,而不是事后再去考慮。無論選擇了哪種技術,最重要的是要防止設計被篡改,無論這個篡改行為是無意的還是非法的。

評論