解讀FPGA設計的安全性

與開發成本很高的ASIC相比,FPGA可重復編程的性能正受到系統設計者的青睞。此外, FPGA的性能和功能也越來越強大,包括32位軟處理器、SERDES、 DSP塊和高性能的接口。現在的低成本FPGA甚至可以滿足大批量的應用。設計人員采用FPGA能夠快速開發產品,以應對產品快速上市(市場要求縮短產品的開發時間)和遠程更新的需求。

本文引用地址:http://www.104case.com/article/192091.htm但是,把器件生產、現場更新和固件遠程重構的工作外包可能會導致FPGA被復制、克隆或盜版。這對某些企業是個嚴重的問題,因為有些算法對企業保持競爭優勢是必不可少的,而外包可能使這些算法被別人利用。因此,考慮FPGA設計的安全性是一件非常重要的事。

FPGA有兩種類型 :基于SRAM、需要用外部引導器件配置的易失FPGA,以及將配置保存在內存中因而不需要外部引導器件的非易失FPGA。基于 SRAM的FPGA是易失器件。如果切斷電源,配置即被刪除,必須對器件進行重新配置,然后器件才能工作。這類器件可以用處理器或使用SPI或并行閃存通過JTAG端口編程。就安全性而言,它們是很脆弱的。一旦系統上電,盜版者就能輕而易舉地獲取FPGA的位流。 Flash和反熔絲FPGA是非易失性的器件,它們上電后即可編程,無需使用任何外部存儲器。這些非易失器件擁有最高級別的安全性。但是,反熔絲FPGA受到兩個方面的制約: 1 )它們不能再次編程。2 )它們的性能和內存容量有限。而Flash FPGA和SRAM FPGA是可以重復編程的。

盜版行為分為幾種類型:“克隆”復制系統元件的行為,甚至不必知道內部的邏輯。通過攔截FPGA的位流和復制配置,可以輕松地克隆一個低成本SRAM FPGA。“逆向工程”需要理解FPGA的邏輯功能,以便進行修改以滿足盜版者的需要。盜版者可以分析無保護的位流以復制原先的設計,或解剖器件分析其內容。還有一個被廣泛使用的盜版手段是“生產超過客戶訂購量的系統”,然后向市場出售多余的系統,而專利持有者卻無法從中取得收益,沒有任何方法可以阻止不擇手段的分包商這樣做。最后一種盜版方法是“盜竊服務”,盜版者通過破解系統的安全設置來獲得特定的服務,如收看衛星電視節目。

打擊盜版可以采用多種安全措施,最簡單的方法的是使用一個保密位,防止FPGA的配置數據被截獲。有了這個保密位,盜版者如果試圖讀取配置數據,讀出的數據將全部為零。所有的FPGA都有這種類型的保護。然而,如果引導文件位于器件的外部,相對就比較容易復制配置,標準的SRAM FPGA就是這種情況 。如果配置數據是在器件內部,如非易失FPGA ,保密位就會有很好的保密效果。

與反熔絲FPGA不同 ,SRAM FPGA和Flash FPGA是可重復編程的,它們允許用戶調整設計或賦予FPGA一個全新的功能。此外,現在甚至可以遠程修改FPGA配置文件,從而修改系統。雖然重構對某些應用來說是個優點,但它也可能成為一個安全隱患,因為盜版者可能攔截并獲取新的碼流。不過這可以通過在傳輸時保護位流來解決。

雖然Flash FPGA比SRAM FPGA更安全 ,它們也有缺點。它們的密度和存儲容量有限,功能和I/O的速度也有限。

針對這些缺點,萊迪思半導體公司已經開發出一種創新的技術,它結合了以下兩種技術的優點:

* 性能和存儲器容量較大的低成本SRAM

* 可以內部存儲重構數據的Flash

萊迪思獨特的flexiFLASH技術,將SRAM和Flash整合在同一個FPGA中,可以同時實現以下幾個方面的優點:

* 位流配置

* 以最短的系統中斷時間進行遠程重新配置

* 數據保護和器件加鎖

復雜系統中的設計安全性

工程師正面臨著構建日益復雜的系統的挑戰。

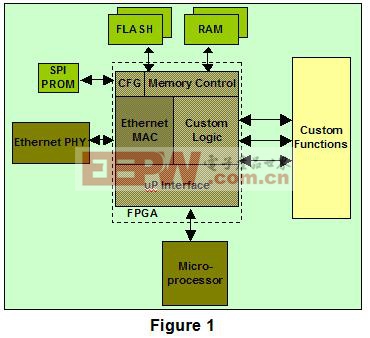

圖1展示了一個FPGA與微處理器相連的系統 。微處理器通過一個外部PHY和一個集成在FPGA內的MAC 與以太網連接。與競爭者的產品不同,這個微處理器中還包含用戶邏輯。 FPGA通過一個Flash來配置。Flash和RAM中包含有微處理器的程序和系統的數據。如果系統需要更新,就通過以太網來發送數據。為了保護設計, FPGA數據和位流都經過了加密。但是,發送到微處理器的數據和指令未加擾,因此盜版者能夠查看此數據并加以復制。一種可能的解決辦法是在FPGA內實現軟微處理器,它可以訪問FPGA的內部存儲器組,而從外部卻無法看到存儲器組。這些存儲器組可以用來存儲重要的算法和數據。

圖1 FPGA與微處理器相連的系統

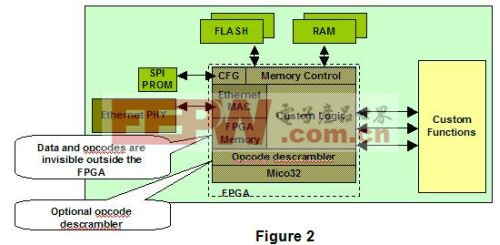

圖2展示了同一個設計,但處理器集成在FPGA之中。圖2中采用的軟微處理器是LatticeMico32 。設計師構建了解擾器,因此加擾是機密的。使用解擾器允許加密的指令存儲在外部存儲器。為了加密位流,萊迪思為幾款FPGA提供了128位AES密鑰。

圖2 處理器集成在FPGA之中

評論