基于SOPC的頻譜分析儀設計與研制

基于NIOS核處理器(包括I2C總線模塊)和Altera公司FPGA設計制作的頻譜分析儀,可用于工程指標的監測和診斷。設計的關鍵模塊有:I2C總線控制的數據采集模塊、FFT模塊、FFT控制模塊、Avalon總線接口及Atlantic總線接口模塊以及VGA、LCD顯示部分。

頻譜分析儀的核心是DFT及快速算法FFT。FFT主要分為基2、基4等固定幾何結構,設計采用基2幾何結構、512點的FFT算法。設計平臺為Altera公司推出的Cvclone II,其為高性能結構體系的PLD器件,其中包括FFT IP Core(知識產權核)。同時,Quartus II(Altera公司開發的IDE)軟件具有很強的硬件仿真和邏輯分析功能,可將Verilog HDL描述的硬件綜合到FPGA的整體設計中。

2 結構設計

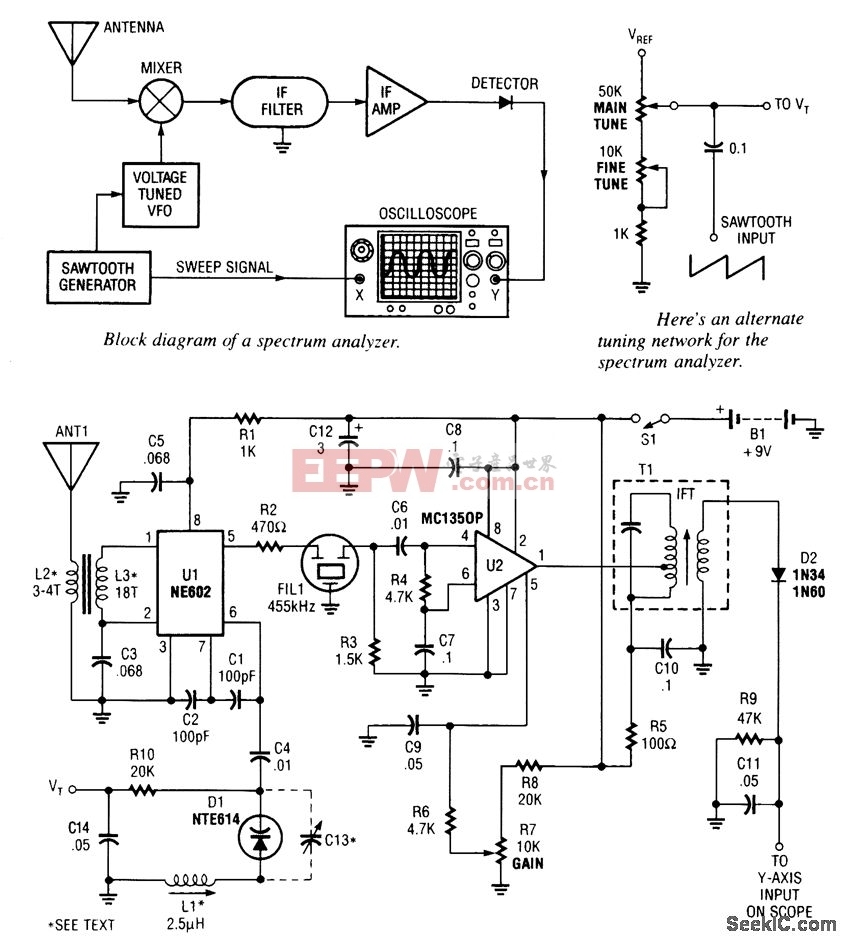

頻譜分析儀的系統框圖如圖1所示,其主要模塊包括:I2C總線模塊、FIFO模塊、平方求和模塊、FFT模塊、VGA模塊、顯示器等組成閉。

頻譜分析儀的硬件原理框圖如圖2所示,圖2包含FPGA的內部硬件電路及外圍接口模塊。

軟件設計的實現是建立在NIOS II IDE的基礎之上,整個軟件設計總體分為4大任務:設計主任務、A/D采集控制、Flash存儲任務和VGA控制顯示器顯示任務。

3 系統設計

設計中,充分利用了SOPC技術的優勢實現軟、硬件協同設計,在盡可能短的時間內實現儀器功能,分別從硬件設計和軟件設計兩方面詳細說明設計過程。

3.1 儀器硬件設計

3.1.1 核設計簡介

利用SOPC Builder在NIOS指令系統中集成了A/D轉換控制、I2C總線控制、VGA控制、FFT控制等控制模塊,圖3為SOPC Builder集成IP。

評論