高速環境下的狀態機設計和優化方法

通過減少寄存器間的邏輯延時來提高工作頻率,或通過流水線設計來優化數據處理時的數據通路來滿足高速環境下FPGA或CPLD中的狀態機設計要求。本文給出了采用這些技術的高速環境狀態機設計的規范及分析方法和優化方法,并給出了相應的示例。

本文引用地址:http://www.104case.com/article/192055.htm為了使FPGA或CPLD中的狀態機設計滿足高速環境要求,設計工程師需要認識到以下幾點:寄存器資源和邏輯資源已經不是問題的所在,狀態機本身所占用的 FPGA或CPLD邏輯資源或寄存器資源非常小;狀態機對整體數據流的是串行操作,如果希望數據處理的延時非常小,就必須提高操作的并行程度,壓縮狀態機中狀態轉移的路徑長度;高速環境下應合理分配狀態機的狀態及轉移條件。本文將結合實際應用案例來說明。

狀態機設計規范

1. 使用一位有效的方式進行狀態編碼

狀態機中狀態編碼主要有三種:連續編碼(sequential encoding)、一位有效(one-hot encoding)方式編碼以及不屬于這兩種的編碼。例如,對于一個5個狀態(State0~State4)的狀態機,連續編碼方式狀態編碼為:State0-000、State1-001、State2-010、State3-011、State4-100。一位有效方式為下為:State0-00001、State1-00010、State2-00100、State3-01000、State4-10000。對于自行定義的編碼則差別很大,例如試圖將狀態機的狀態位直接作為輸出所需信號,這可能會增加設計難度。

使用一位有效編碼方式使邏輯實現更簡潔,因為一個狀態只需要用一位來指示,而為此增加的狀態寄存器數目相對于整個設計來說可以忽略。一位有效至少有兩個含義:對每個狀態位,該位為1對應唯一的狀態,判斷當前狀態是否為該狀態,只需判斷該狀態位是否為1;如果狀態寄存器輸入端該位為1,則下一狀態將轉移為該狀態,判斷下一狀態是否為該狀態,只需判斷表示下一狀態的信號中該位是否為1。

2. 合理分配狀態轉移條件

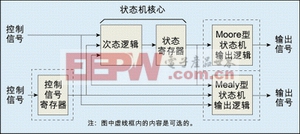

在狀態轉移圖中,每個狀態都有對應的出線和入線,從不同狀態經不同的轉移條件到該狀態的入線數目不能太多。以采用與或邏輯的CPLD設計來分析,如果這樣的入線太多則將會需要較多的乘積項及或邏輯,這就需要更多級的邏輯級聯來完成,從而增加了寄存器間的延遲;對于FPGA則需要多級查找表來實現相應的邏輯,同樣會增加延遲。狀態機的應用模型如圖1所示。

狀態機設計的分析方法

狀態機設計的分析方法可以分為兩種:一種是流程處理分析,即分析數據如何分步處理,將相應處理的步驟依次定為不同狀態,該方法能夠分析非常復雜的狀態機,類似于編寫一個軟件程序的分析,典型設計如讀寫操作和數據包字節分析;另一種方法是關鍵條件分析,即根據參考信號的邏輯條件來確定相應的狀態,這樣的參考信號如空或滿指示、起始或結束、握手應答信號等。這兩種分析方法并沒有嚴格的界限,在實際的狀態機設計分析時往往是這兩種方法結合使用。下面分別說明這兩種分析方法。

1. 流程處理分析

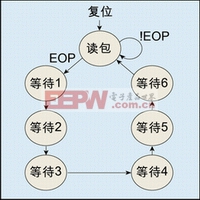

例如,在一個讀取ZBT SRAM中數據包的設計中,要根據讀出的數據中EOP(End of Packet)信號是否為1來決定一個包的讀操作是否結束,由于讀取數據的延后,這樣就會從ZBT SRAM中多讀取數據,為此可以設計一個信號VAL_out來過濾掉多讀的數據。

根據數據到達的先后及占用的時鐘周期數,可以設計如圖2所示的狀態機(本文設定:文字說明及插圖中當前狀態表示為s_State[n:0],為狀態寄存器的輸出;下一狀態next_State[n:0],為狀態寄存器的輸入;信號之間的邏輯關系采用Verilog語言(或C語言)中的符號表示;#R表示需要經過一級寄存器,輸出信號對應寄存器的輸出端)。該狀態機首先判斷是否已經到達包尾,如果是,則依次進入6個等待狀態,等待狀態下的數據無效,6個等待狀態結束后將正常處理數據。

2. 關鍵條件分析

一個路由器線卡高速數據包分發處理的框圖,較高速率的數據包經過分發模塊以包為單位送往兩個較低速率數據通路(即寫入FIFO1或FIFO2)。

評論