利用FPGA的新功能保證視頻設(shè)計(jì)安全性

DeviceDNA允許設(shè)備生產(chǎn)商將一個(gè)獨(dú)一無二的非易失工廠序列號(hào)直接寫入到FPGA器件中。每個(gè)器件的ID都不同,因此可以將設(shè)計(jì)綁定到特定的FPGA器件中。DeviceDNA可以作為接收設(shè)備的獨(dú)特序列號(hào),一個(gè)唯一的許可代碼,或者與用戶定義的寫在FPGA構(gòu)造中的認(rèn)證算法配合使用,從而將特定的設(shè)計(jì)與特定FPGA器件緊密綁定在一起。如果某些人試圖克隆或拷貝認(rèn)證過的設(shè)計(jì),或者將位流寫入另一片不同的FPGA器件,那么由于器件的ID號(hào)碼變化,設(shè)計(jì)就不會(huì)通過認(rèn)證。DeviceDNA是一個(gè)57位長的序列號(hào),可以通過器件內(nèi)部的邏輯構(gòu)造讀取。

DeviceDNA與用戶定義認(rèn)證算法緊密結(jié)合能夠以合理的系統(tǒng)成本實(shí)現(xiàn)所需要的安全度。在采用認(rèn)證算法的方法中,安全性的關(guān)鍵是算法本身。在本方法中,安全過程中必須有某些部分要保密,在本案例中則是用戶定義的算法本身。由于算法在PPGA邏輯構(gòu)造中實(shí)現(xiàn),因此成為FPGA數(shù)百萬配置位中的少數(shù)位。除非知道這些位如何組合在一起,或者知道算法本身,否則參于任何試圖拷貝設(shè)計(jì)的人來說,看起來都僅僅是一堆數(shù)字。

用戶定義的算法可以如系統(tǒng)所需要的一樣簡單或復(fù)雜 - 例如:可以是簡單的哈希算法,或者更為復(fù)雜的三次DES、AES6?、128或256位,甚至是完全定制的算法。同時(shí)還可以將用戶定義的認(rèn)證算法集成到接收器的認(rèn)證流程內(nèi)部。這樣可以進(jìn)一步將接收單元與視頻流系統(tǒng)、設(shè)計(jì)與特定的接收單元捆綁在一起,從而進(jìn)一步提高抵抗克隆的安全能力。此外,算法可以改變以支持不同的視頻解密協(xié)議配置,甚至在不同型號(hào)或不同代產(chǎn)品間采用不同的算法,從而進(jìn)一步保證安全性。

安全性提高對(duì)生產(chǎn)的影響

硬件安全性問題同樣適用于生產(chǎn)流程,特別是板級(jí)測(cè)試和驗(yàn)證。因此,設(shè)計(jì)中經(jīng)常將JTAG功能移除,因?yàn)镴TAG功能易使設(shè)計(jì)導(dǎo)致反向工程。許多企業(yè)都采用JTAG來縮短測(cè)試時(shí)間并提高測(cè)量和驗(yàn)證流程中的系統(tǒng)測(cè)試覆蓋范圍。然而,沒有JTAG,就需要更多的測(cè)試,特別是系統(tǒng)級(jí)測(cè)試來保證一定的測(cè)試覆蓋范圍。不使用JTAG技術(shù)會(huì)提高生產(chǎn)成本,并最終影響到系統(tǒng)總成本。

JTAG的問題在于INTEST命令,用于檢查設(shè)計(jì)的內(nèi)部邏輯功能。反向工程時(shí),這一命令可用來判斷設(shè)計(jì)的功能。圖3給出了一個(gè)簡單的例子,其中數(shù)據(jù)移入寄存器,執(zhí)行INTEST命令,這樣數(shù)據(jù)會(huì)在時(shí)鐘作用下移入邏輯構(gòu)造,進(jìn)入下一寄存器,結(jié)果可以被讀出。由于可將總體設(shè)計(jì)的復(fù)雜度縮小到更小的邏輯模塊,因此這一命令可使反向工程的工作更容易。

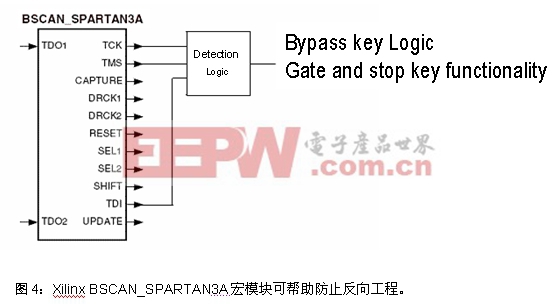

一些FPGA平臺(tái)可幫助防止發(fā)生這一過程,同時(shí)仍然允許生產(chǎn)商完成其管腳至管腳(pin-to-pin)功能。例如,在Xilinx? Spartan?-3A 平臺(tái)中, 可在設(shè)計(jì)中使用BSCAN_SPARTAN3A宏模塊,其檢測(cè)邏輯可監(jiān)控FPGA構(gòu)造中的JTAG控制信號(hào),如圖4所示。如果檢測(cè)到JTAG控制信號(hào)的活動(dòng),用戶在設(shè)計(jì)可以立即繞過關(guān)鍵邏輯或關(guān)斷關(guān)鍵功能,不再執(zhí)行正確的功能。這樣反向工程人員讀到的將是不正確的功能模塊,在不能完成預(yù)期功能的解決方案上浪費(fèi)時(shí)間和資源。

支持DeviceDNA的FPGA平臺(tái)可保證視頻接收機(jī)的設(shè)計(jì)安全,同時(shí)還可為測(cè)試和驗(yàn)證流程提供支持,從而能夠提供成本經(jīng)濟(jì)的高質(zhì)量安全解決方案,支持多種不同的視頻流加密協(xié)議。

評(píng)論