基于FPGA的DVI/HDMI接口實現

基于ECP2M的接收功能實現本文引用地址:http://www.104case.com/article/192045.htm

DVI/HDMI參考設計有發送和接收功能。在接收端,ECP2M利用內置模塊SERDES恢復T M D S信號,通過SERDES內的時鐘和數據恢復(CDR)電路完成這個處理。CDR電路將每個串行的T M D S通道轉換至10位,并將具有同步時鐘的數據傳送至FPGA接口,然后在FPGA中進行數據處理達到同步。這要求有三個級別的同步,分別是在本文中稱為“字節對齊”的10位同步、通道調整、多通道對齊。文章的后面討論這些步驟。接下來是自動檢測正在運行的數據流的分辨率(480p、720p、1080p或1080i),并調整物理編碼子層(PCS)參數。當在這些分辨率之間動態切換時,應保證優化運行。針對發送端,沒有必要進行字節和通道對齊。10位模式的PCS是用來使數據串行化,并與液晶顯示屏通信。

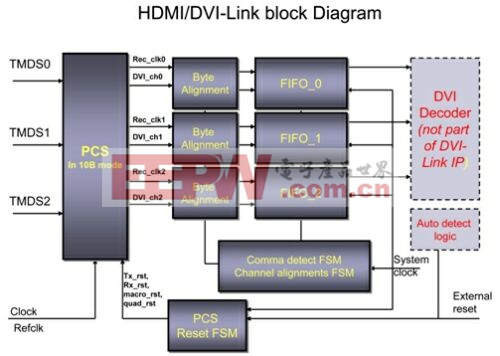

ECP2M/ECP3的CML SERDES輸入(見圖3的接收信號流)收到T M D S三個通道的信號(0、1,和2)數據。由于DVI/HDMI的信號不采用標準的8B/10B編碼,SERDES后面的PCS設置成10位模式(旁路)。T M D S信號傳輸使用對本協議唯一的四個對齊的字符(不同于8B/10B方式)。串行器與SERDES的CDR傳遞10位的原始數據,FPGA進行字節對齊。DVI/HDMI鏈路連接能以多個不同的頻率發送數據,自動檢測邏輯被用來檢測正在傳送的是哪種分辨率,并配置PCS以便在SERDES鎖相環中實現鎖定。

圖3:HDMI/DVI鏈路的原理框圖。

接收同步

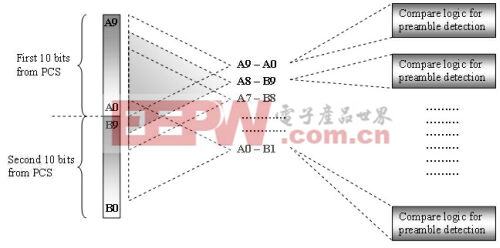

一旦10位數據在FGPA中,執行上述定義的三個步驟(字節對齊、通道對齊、多通道對齊)是必須的 。字節對齊:設計確定在數據流的哪里是10位數據字節的開始和結束。在FPGA結構中使用有限狀態機(FSM)來完成這一任務。把數據流的第一個和第二個10位組合在一起,形成一個20位的總線;然后分解至9位、10位總線。在這一階段,數據與對齊的字符進行比較,當字符順序發生了8次(稱為單通道對齊),同步信號有效。狀態圖如圖4所示。

圖4:接收同步的狀態圖。

同步檢測之后,對齊數據的字節寫入FIFO。當所有三個通道都完成了“通道對齊”,就可以寫入FIFO,至此通道對齊的任務就結束了。在這一階段, FPGA將等待直到FIFO處于半滿狀態,并在同一時間(多通道對齊)對三個FIFO進行讀操作 。這將保證三個通道對齊,并同步。

評論