基于FPGA的音頻編解碼芯片接口設(shè)計(jì)

摘 要:24位立體聲音頻編解碼芯片WM8731因其高性能、低功耗等優(yōu)點(diǎn)在很多音頻產(chǎn)品中得到了廣泛應(yīng)用。介紹了其基于FPGA的接口電路的設(shè)計(jì),包括芯片配置模塊與音頻數(shù)據(jù)接口模塊等,使得控制器只通過寄存器就可以方便地對其進(jìn)行操作,而不需要考慮其接口電路復(fù)雜的時鐘時序問題,從而有效地降低了利用此芯片的難度。整個設(shè)計(jì)以VHDL和Verilog HDL語言在Max+Plus Ⅱ里實(shí)現(xiàn),并進(jìn)行了驗(yàn)證,結(jié)果表明能滿足使用者的要求且操作簡單。對其他編解碼芯片的接口設(shè)計(jì)也有一定的參考作用。

關(guān)鍵詞:WM8731;FPGA;接口設(shè)計(jì);音頻編解碼芯片

1 概 述

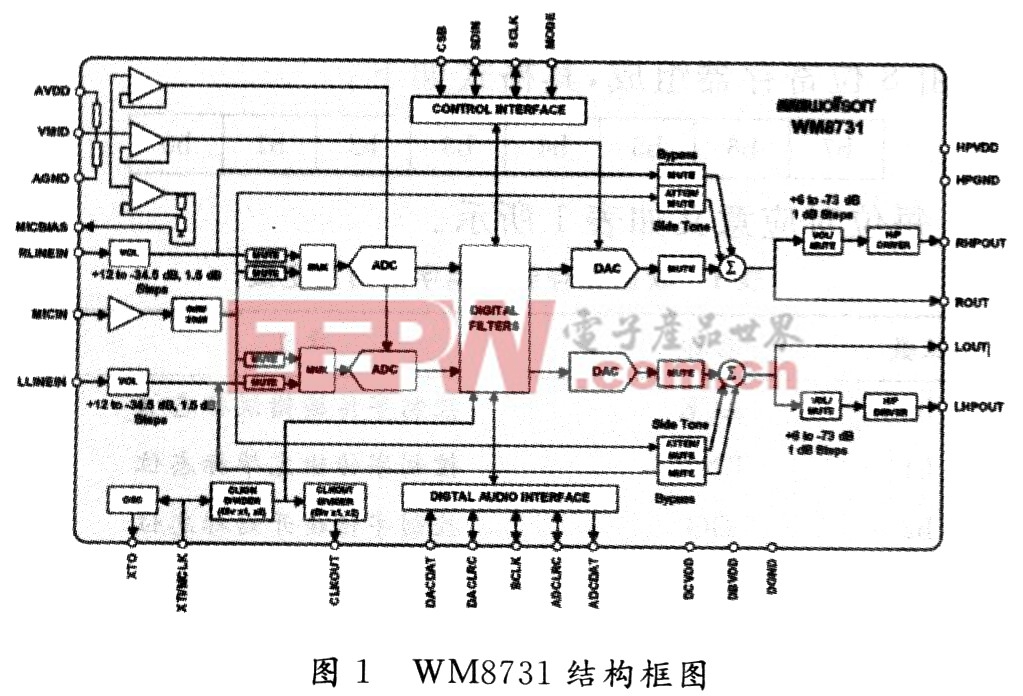

WM873l是一款功能強(qiáng)大的低功耗立體聲24位音頻編解碼芯片,其高性能耳機(jī)驅(qū)動器、低功耗設(shè)計(jì)、可控采樣頻率、可選擇的濾波器使得WM8731芯片廣泛使用于便攜式MP3,CD,PDA的場合。其結(jié)構(gòu)框圖如圖1所示。

WM8731包含2個線路輸入和1路麥克風(fēng)輸入并可以進(jìn)行音量調(diào)節(jié);內(nèi)置片上ADC(模擬數(shù)字轉(zhuǎn)換器)及可選擇的高通數(shù)字濾波器;采用高品質(zhì)過采樣率結(jié)構(gòu)的DAC(數(shù)字模擬轉(zhuǎn)換器);線路輸出和耳機(jī)輸出;內(nèi)置晶體振蕩器以及可配置的數(shù)字音頻接口和2或3線可選的微處理器控制接口等。控制器可通過控制接口(Control Interface)對WM8731進(jìn)行配置,然后通過數(shù)字音頻接口(Digtal Audio Interface)讀寫數(shù)據(jù)音頻信號。本文設(shè)計(jì)了一種基于FPGA的驅(qū)動模塊,將WM8731的控制接口與數(shù)字音頻接口轉(zhuǎn)換為控制器通用的總線接口,使控制器可以像讀寫外部寄存器一樣對WM8731芯片進(jìn)行控制使用。

2 WM8731芯片接口時序介紹

2.1 控制接口時序

WM8731的控制接口有4根引腳,分別為:MODE(控制接口選擇線)、CSB(片選或地址選擇線)、SDIN(數(shù)據(jù)輸入線)和SCLK(時鐘輸入線)。它具有2線和3線兩種模式。2線為MPU接口,3線為兼容SPI接口。對控制接口的配置選擇可通過設(shè)置MODE腳的狀態(tài)完成。選擇MODE為0時為2線模式,1時為3線模式。本文采用2線模式對WM8731進(jìn)行控制。其時序圖如圖2所示。

2.2 數(shù)字音頻接口時序

WM8731的數(shù)字音頻接口有5根引腳,分別為:BCLK(數(shù)字音頻位時鐘)、DACDAT(DAC數(shù)字音頻數(shù)據(jù)輸入)、DACIRC(DAC采樣左/右聲道信號)、ADC-DAT(ADC數(shù)字音頻信號輸出)、ADCLRC(ADC采樣左/右聲道信號)。

數(shù)字音頻接口可以工作在主模式和從模式下。地址為0000111的寄存器的第6位設(shè)置數(shù)據(jù)的主/從模式:“1”為主模式,“0”為從模式。ADCDAT、/DACDAI和ADCLRC/DACLRC與位時鐘BCIK同步,在每個BCLK的下降沿進(jìn)行一次傳輸。BCLK和ADCLRC/DACLRC在主模式時為輸出信號,從模式下為輸入信號。DAC-DAT始終為輸入信號,ADCDAT始終為輸出信號。

評論