高速FPGA系統的信號完整性測試和分析

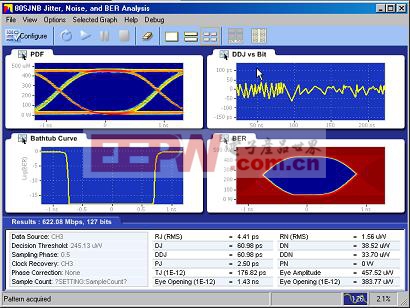

80SJNB軟件除了能夠得到每一個抖動和噪聲分量的精確結果,針對設計和測試人員還提供了各種圖形顯示進行更細致的信號完整性分析。例如,抖動和噪聲成分概率分布, 頻譜分布, 數據相關抖動和噪聲與位的關系, 數據碼型波形, 抖動和噪聲浴缸曲線, BER概率圖, BER輪廓圖, 概率分布眼圖。圖5是得到的分析結果。本文引用地址:http://www.104case.com/article/192023.htm

圖5 80SJNB軟件得到的分析結果

5. 高速并行總線的眼圖測試

對于FPGA芯片提供的高速并行總線,由于其數據傳送方式并沒有采用內嵌時鐘的方法,時鐘可以作為觸發信號,觀測多路并行總線的眼圖。由于并行總線的通道數比較多,在示波器中手工測試多通道的眼圖比較繁瑣,有些傳統邏輯分析儀雖然能夠直接進行并行總線的眼圖測試,但無論是測試精度和速度都無法和示波器進行的標準眼圖測試相提并論。

除了能夠通過FPGAView對簡化FPGA的在線調試,TLA邏輯分析儀能夠配合TDS示波器對FPGA外部信號自動進行多通道的眼圖測試和分析,該功能稱為iVerify眼圖測試,最多可以自動的測試408個通道的眼圖。

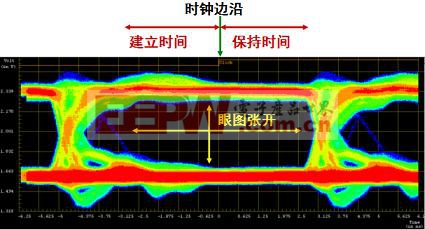

泰克為邏輯分析儀和示波器集成提供了一個信號完整性測試工具包,稱為iLink工具包,分為iConnect,iView,以及iVerify眼圖測試三個工具。iVerify是建立在iConnect技術和iView技術的基礎上,它能夠自動對多路并行總線進行眼圖測試來徹底驗證被測信號。結合iConnect技術,使用一套邏輯分析儀有源探頭進行信號邏輯和模擬的同時觀測,邏輯分析儀可以將被測通道分成多組,每一組3個數據通道送入到示波器中進行眼圖測試,示波器的第4個通道作為外部時鐘;采用iView技術,邏輯分析儀可以自動的將每一次送入示波器的3個數據信號的眼圖測試數據會傳到邏輯分析儀中,這樣邏輯分析儀就可以再選擇另外一組3個通道進行測試,對于復雜的高速總線,可以一次測試408個數據通道。最后,iVerify技術通過邏輯分析儀將最多408個數據信號的眼圖測試數據疊加顯示出來,徹底驗證總線中出現的信號完整性問題。圖6是在TLA邏輯分析儀上自動累計的多個通道眼圖數據的色溫顯示。

圖6 TLA邏輯分析儀上顯示多通道眼圖測試結果

6. 小結

對于FPGA中的高速串行和并行IO信號,需要根據被測信號特點和速度來選擇合適的測試和分析工具。當測試信號完整性,希望得到最精確的上升時間,下降時間,信號過沖和震鈴等參數,帶寬是首要選擇。某種意義上帶寬越高,測試精度越高。對于實時示波器而言,高速采集內存是眼圖和抖動等信號完整性測試的關鍵。對于采樣示波器,通過CSA/TDS8200配合80SJNB抖動和噪聲分析軟件,不僅可以精確的測量高速串行信號的抖動和噪聲,并且能夠根據測量結果進行精確的抖動、噪聲中每一個分量的分離,和系統的BER相關,最終為信號完整性驗證人員提供有價值的信息。當測試高速時鐘或數據抖動時,泰克兩種示波器都配備業內推薦的抖動測試和分析軟件,幫助設計人員得到抖動結果,分析抖動產生的原因,最終得到高可靠性的系統。

評論