高速FPGA系統的信號完整性測試和分析

泰克TDS6154C高速實時示波器采用硅鍺(SiGe)半導體集成采集前端,并使用獨立的高速存儲器,這樣就不受內存長度的限制,并且它同時支持最大采樣率和存儲長度。

針對FPGA中不斷增長的串行數據傳輸速率,設計人員不僅進行眼圖測試,還需要一套先進的測試和分析工具幫助他們更好地理解和改善他們設計方案的信號完整性。

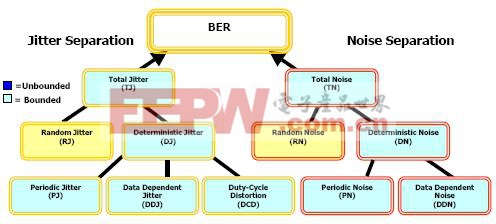

針對FPGA提供的各種高速串行信號,傳統的采樣示波器配合抖動分析軟件針對FPGA中的高速串行信號能夠進行抖動的測試,測試結果的分離,后期的抖動原因的定位和分析,以及水平時間分量上的BER分析。但是,對于導致BER的另一個主要原因,即串行信號中的噪聲分量,沒有一個徹底的測試和分析方法。圖4顯示了對于一個高速串行信號的抖動分量和噪聲分量影響BER的過程。

圖4 抖動分量和噪聲分量的分解

從事FPGA器件的設計和應用,以及背板的設計和制造的公司在開發基于超高速串行數據標準的產品時需要最高精度的抖動分析,噪聲分析以及完整的BER眼圖信息。泰克CSA/TDS8200系列采樣示波器 (Sampling Oscilloscope)測試眼圖時,除了傳統的眼圖和抖動測試外,泰克80SJNB抖動和噪聲分析軟件提供了對于設計人員和調試人員更有價值的抖動、噪聲、BER分析功能。

80SJNB不僅能夠得到高精度的眼圖測試結果,還能夠通過分隔抖動和噪聲,加快了識別水平和垂直眼圖閉合原因的速度。由于它能夠以獨特的視角查看抖動和噪聲的構成成分,80SJNB可以高度精確全面地推斷BER及分析眼圖輪廓。在把抖動、噪聲和BER分析與8000系列的模塊化靈活性、完善的性能和信號保真度結合在一起時,您可以獲得理想的下一代高速串行數據設計檢驗和一致性測試解決方案。下表列出了80SJNB軟件配合泰克CSA/TDS8200系列示波器得到的抖動和噪聲分析結果。

評論